# HT Series<sup>™</sup> MTX Series<sup>™</sup> PRO Series<sup>™</sup>

MOTOROLA

Professional Series Two-Way Portable Radios

**Detailed Service Manual**

# **Document History**

The following major changes have been implemented in this manual since the previous edition:

| Edition      | Description                                                                                                                                                             | Date       |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 6881088E46-E | The Theory of Operation section has been divided into the following six sections: Distribution Keypad UHF Band 1 UHF Band 2 VHF Lowband, 800 MHz, PassPort, and 900 MHz | July, 2005 |

|              | Troubleshooting Flow Charts in the Maintenance section have updated.                                                                                                    |            |

|              | Added 8480587Z05 to UHF Band 1                                                                                                                                          |            |

|              | Added 8480450Z14 to UHF Band 1                                                                                                                                          |            |

|              | Added 8486458Z02 to UHF Band 1                                                                                                                                          |            |

|              | Added 8486458Z03 to UHF Band 1                                                                                                                                          |            |

|              | Added 8415234H01 to UHF Band 1                                                                                                                                          |            |

|              | Added 8485677Z03 to UHF Band 2                                                                                                                                          |            |

|              | Added 8486686Z01 to UHF Band 2                                                                                                                                          |            |

|              | Added 8486686Z02 to UHF Band 2                                                                                                                                          |            |

|              | Added 8415235H01 to UHF Band 2                                                                                                                                          |            |

|              | Added 8486062B16 to VHF                                                                                                                                                 |            |

|              | Added 8486062B17 to VHF                                                                                                                                                 |            |

|              | Added 8486101B11 to VHF                                                                                                                                                 |            |

|              | Added 8486473Z03 to VHF                                                                                                                                                 |            |

|              | Added 8486473Z04 to VHF                                                                                                                                                 |            |

|              | Added 8415112H01 to VHF                                                                                                                                                 |            |

HT Series<sup>™</sup>

MTX Series<sup>™</sup>

PRO Series<sup>™</sup>

Professional Series

Two-Way Portable Radio

Detailed Service Manual

#### **Foreword**

The information contained in this manual relates to all models of the Professional Series two-way portable radios, unless otherwise specified. This manual provides sufficient information to enable qualified service shop technicians to troubleshoot and repair portable radios to the component level.

For details on the level 1 or 2 maintenance procedures, refer to the applicable manuals, which are available separately. A list of publications is provided in this manual in the section, "1.3 Related Documents" on page 1-2.

#### **Product Safety and RF Exposure Compliance**

Before using this product, read the operating instructions for safe usage contained in the Product Safety and RF Exposure booklet enclosed with your radio.

#### ATTENTION!

This radio is restricted to occupational use only to satisfy FCC RF energy exposure requirements. Before using this product, read the RF energy awareness information and operating instructions in the Product Safety and RF Exposure booklet enclosed with your radio (Motorola Publication part number 6881095C98) to ensure compliance with RF energy exposure limits.

For a list of Motorola-approved antennas, batteries, and other accessories, visit the following web site which lists approved accessories: <a href="http://www.motorola.com/cgiss/index.shtml">http://www.motorola.com/cgiss/index.shtml</a>

#### **Manual Revisions**

Changes which occur after this manual is printed are described in FMRs (Florida Manual Revisions). These FMRs provide complete replacement pages for all added, changed, and deleted items, including pertinent parts list data, schematics, and component layout diagrams.

#### **Computer Software Copyrights**

The Motorola products described in this manual may include copyrighted Motorola computer programs stored in semiconductor memories or other media. Laws in the United States and other countries preserve for Motorola certain exclusive rights for copyrighted computer programs, including, but not limited to, the exclusive right to copy or reproduce in any form the copyrighted computer program. Accordingly, any copyrighted Motorola computer programs contained in the Motorola products described in this manual may not be copied, reproduced, modified, reverse-engineered, or distributed in any manner without the express written permission of Motorola. Furthermore, the purchase of Motorola products shall not be deemed to grant either directly or by implication, estoppel, or otherwise, any license under the copyrights, patents or patent applications of Motorola, except for the normal non-exclusive license to use that arises by operation of law in the sale of a product.

#### **Document Copyrights**

No duplication or distribution of this document or any portion thereof shall take place without the express written permission of Motorola. No part of this manual may be reproduced, distributed, or transmitted in any form or by any means, electronic or mechanical, for any purpose without the express written permission of Motorola.

#### **Disclaimer**

The information in this document is carefully examined, and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, Motorola reserves the right to make changes to any products herein to improve readability, function, or design. Motorola does not assume any liability arising out of the applications or use of any product or circuit described herein; nor does it cover any license under its patent rights nor the rights of others.

#### **Trademarks**

MOTOROLA and the Stylized M logo are registered in the US Patent & Trademark Office. All other products or service names are the property of their respective owners.

© Motorola, Inc. 2005.

Table of Contents iii

# **Table of Contents**

| Forev                                              | vord                                             |                                      | ii               |

|----------------------------------------------------|--------------------------------------------------|--------------------------------------|------------------|

| Mar<br>Con<br>Doc<br>Disc<br>Trac<br><b>List o</b> | nual Revi<br>nputer Socument Colaimer<br>demarks | ety and RF Exposure Compliance       | i<br>i<br>i<br>i |

| Intrin                                             | sically                                          | Safe Radio Information               | xix              |

|                                                    |                                                  | oved Equipment                       |                  |

| Rep                                                |                                                  | IRC Approved Products                |                  |

|                                                    |                                                  | . Line and                           |                  |

| Da l                                               |                                                  | eling                                |                  |

| ו סט                                               | INOT SUDS                                        | stitute Options or Accessories       | XX               |

| Chap                                               | ter 1                                            | Introduction                         | 1-1              |

| 1.1                                                | Scope                                            | of Manual                            | 1-1              |

| 1.2                                                | Warrar                                           | nty and Service Support              | 1-1              |

|                                                    | 1.2.1                                            | Warranty Period                      |                  |

|                                                    | 1.2.2                                            | Return Instructions                  |                  |

| 4.0                                                | 1.2.3                                            | After Warranty Period                |                  |

| 1.3                                                |                                                  | d Documents                          |                  |

| 1.4                                                | 1 echni<br>1.4.1                                 | ical SupportPiece Parts Availability |                  |

| 1.5                                                |                                                  | Model Chart and Specifications       |                  |

| 1.6                                                |                                                  | Model Information                    |                  |

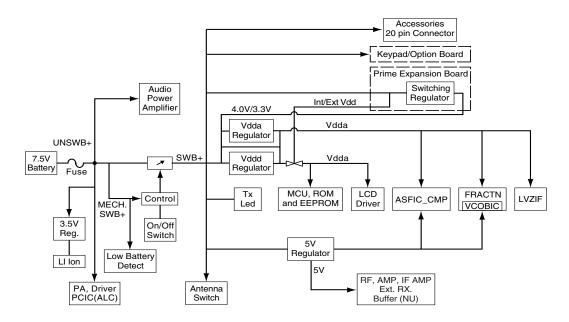

| Chap                                               |                                                  | Radio Power Distribution             |                  |

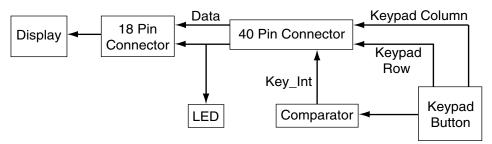

| Chap                                               |                                                  | Keypad                               |                  |

| -                                                  |                                                  |                                      |                  |

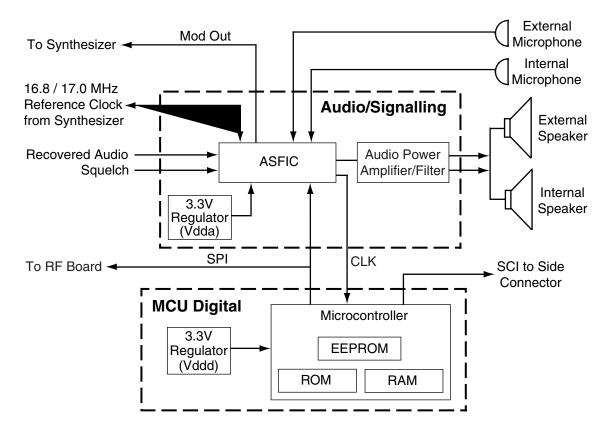

| 3.1                                                | 3.1.1                                            | ller BoardMCU Digital                |                  |

|                                                    | 3.1.1                                            | Real Time Clock                      |                  |

|                                                    | 3.1.2                                            | Circuit Description                  |                  |

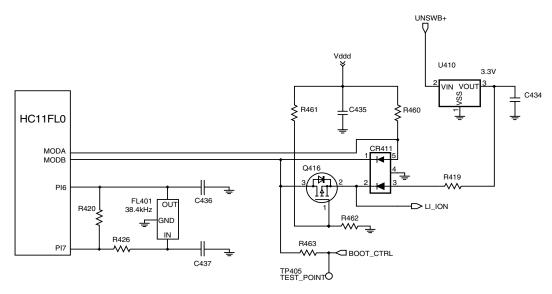

|                                                    | 3.1.4                                            | MODB/VSTBY Supply                    |                  |

|                                                    | 3.1.5                                            | Audio/Signaling                      |                  |

iv Table of Contents

| Chapter 4 |        | UHF Band 1 Theory of Operation                        | 4-1 |

|-----------|--------|-------------------------------------------------------|-----|

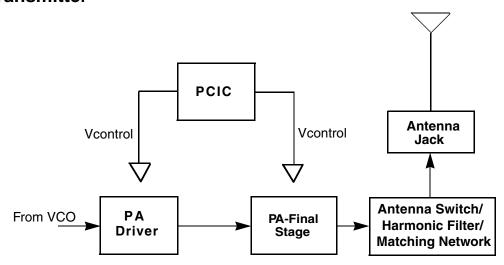

| 4.1       | Transı | mitter                                                | 4-1 |

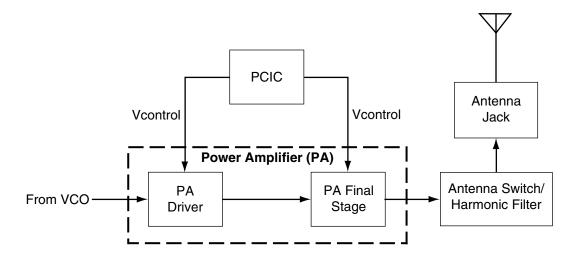

|           | 4.1.1  | General                                               | 4-1 |

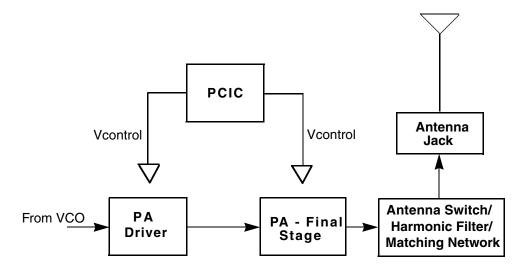

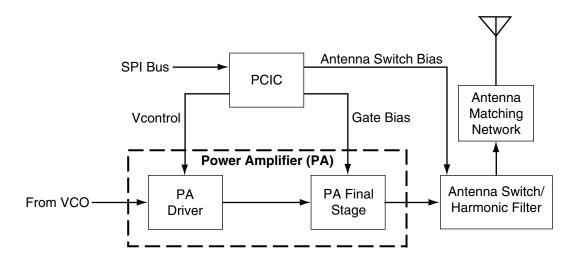

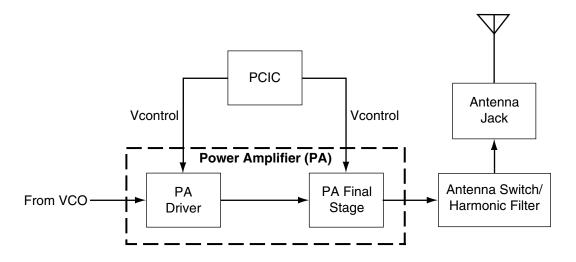

|           | 4.1.2  | Power Amplifier                                       | 4-1 |

|           | 4.1.3  | Antenna Switch                                        |     |

|           | 4.1.4  | Harmonic Filter                                       | 4-2 |

|           | 4.1.5  | Antenna Matching Network                              | 4-2 |

|           | 4.1.6  | Power Control Integrated Circuit (PCIC)               | 4-2 |

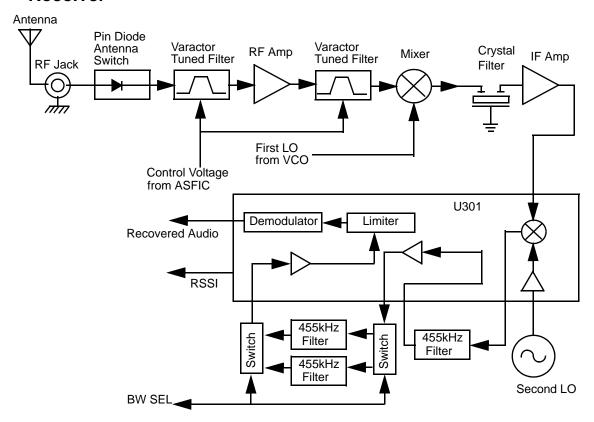

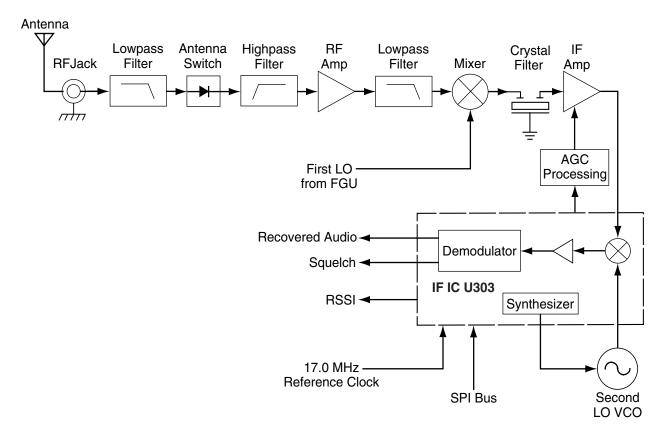

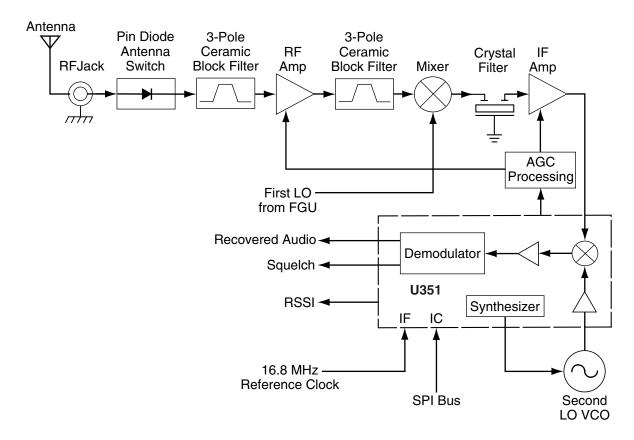

| 4.2       | Receiv | ver                                                   | 4-3 |

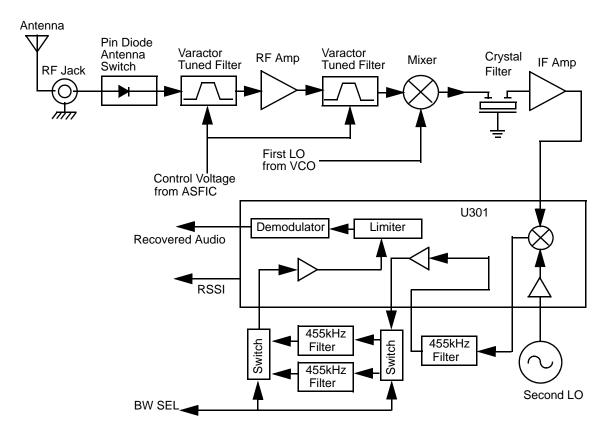

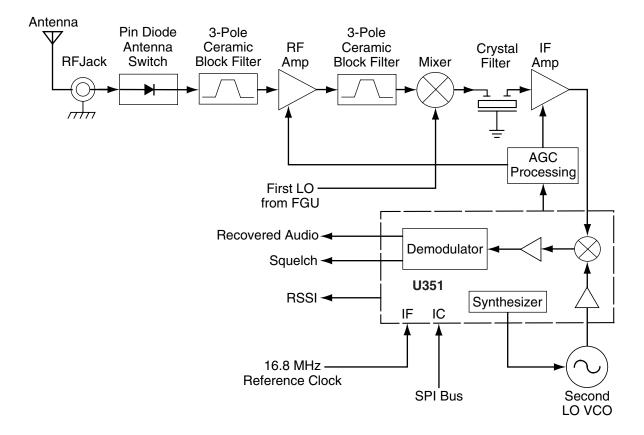

|           | 4.2.1  | Receiver Front-End                                    | 4-3 |

|           | 4.2.2  | Receiver Back-End                                     | 4-4 |

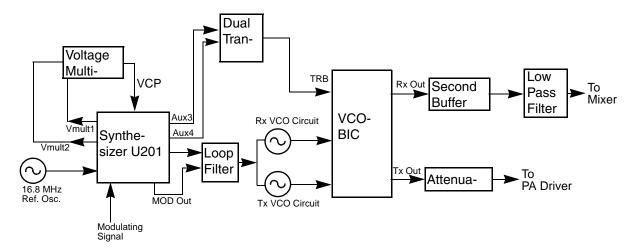

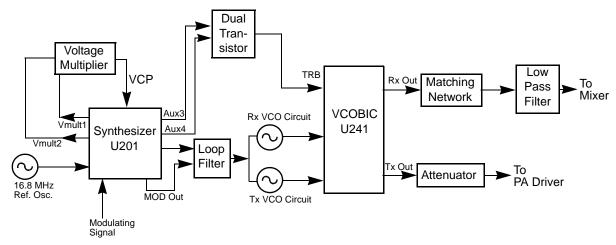

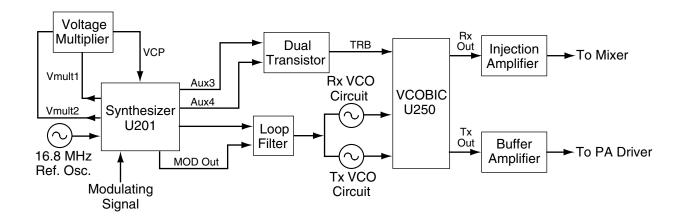

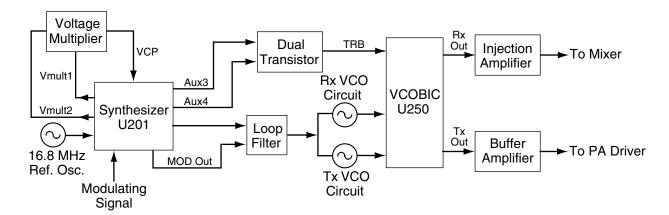

| 4.3       | Freque | ency Generation Circuitry                             | 4-4 |

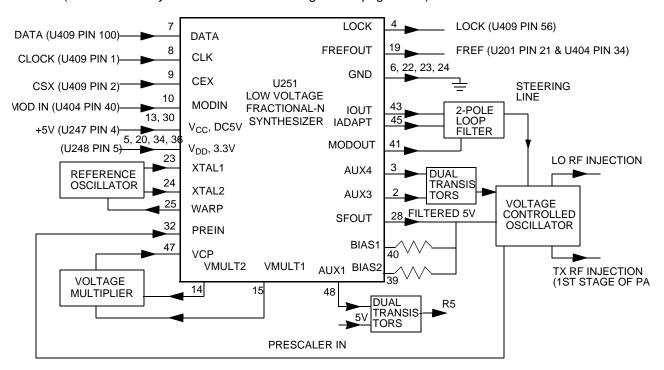

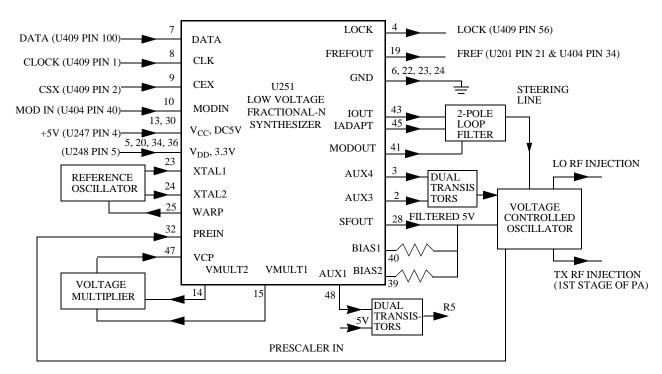

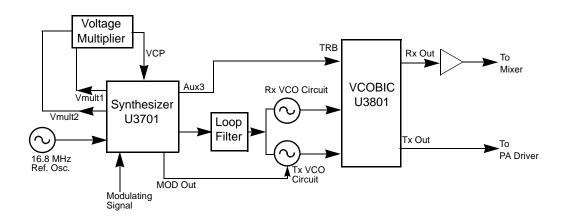

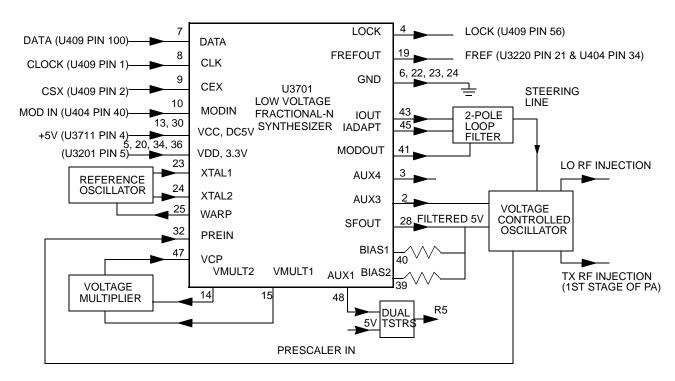

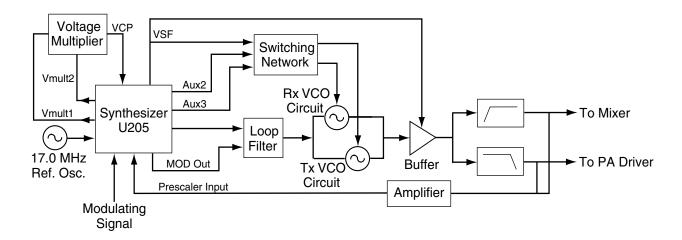

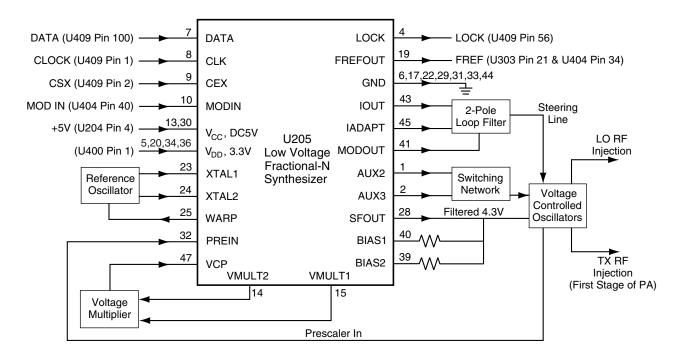

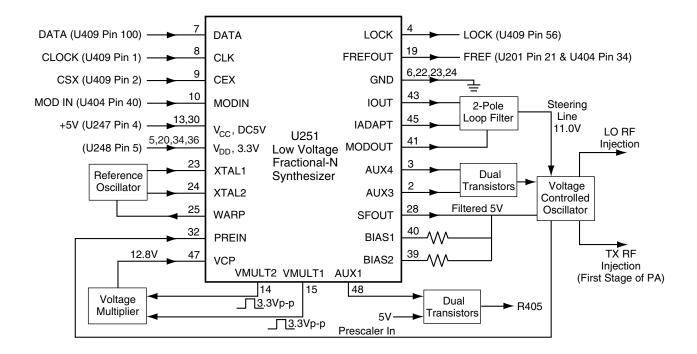

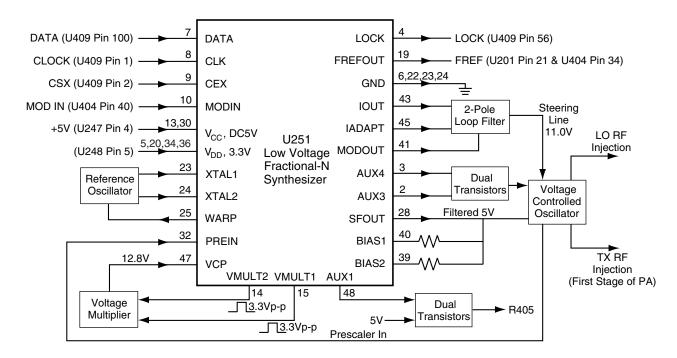

| 4.4       | Synthe | esizer                                                | 4-5 |

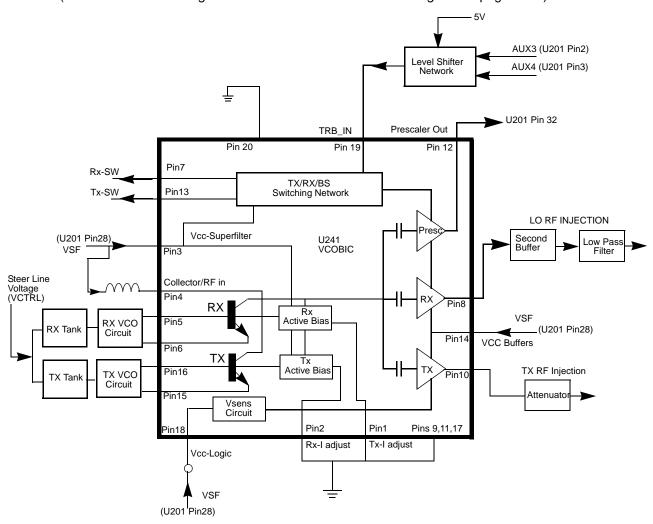

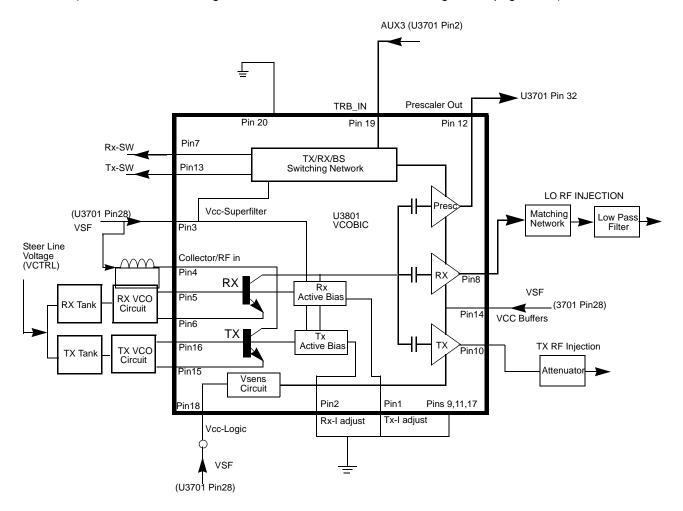

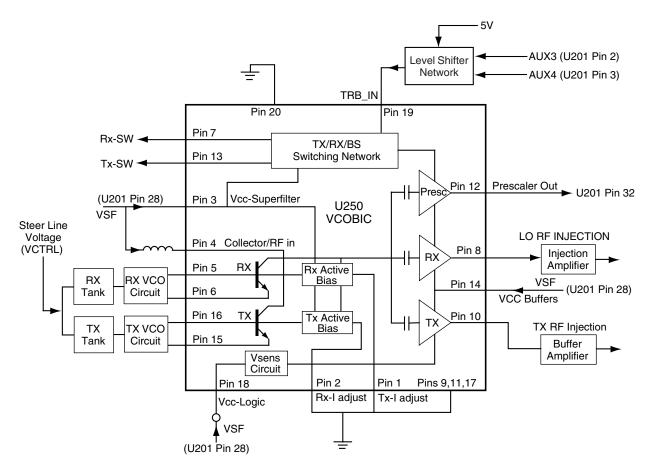

| 4.5       | Voltag | ge-Controlled Oscillator (VCO)                        | 4-6 |

| Chapt     | er 5   | UHF Band 2 Theory of Operation                        | 5-1 |

| 5.1       | Transı | mitter                                                | 5-1 |

|           | 5.1.1  | General                                               | 5-1 |

|           | 5.1.2  | Power Amplifier                                       | 5-1 |

|           | 5.1.3  | Antenna Switch                                        | 5-2 |

|           | 5.1.4  | Harmonic Filter                                       | 5-2 |

|           | 5.1.5  | Antenna Matching Network                              | 5-2 |

|           | 5.1.6  | Power Control Integrated Circuit (PCIC)               | 5-2 |

| 5.2       | Receiv | ver                                                   | 5-3 |

|           | 5.2.1  | Receiver Front-End                                    | 5-3 |

|           | 5.2.2  | Receiver Back-End                                     | 5-3 |

| 5.3       | Freque | ency Generation Circuitry                             | 5-4 |

| 5.4       | Synthe | esizer                                                | 5-5 |

| 5.5       | Voltag | ge-Controlled Oscillator (VCO)                        | 5-6 |

| Chapt     | er 6   | VHF Theory of Operation                               | 6-1 |

| 6.1       | Transı | mitter                                                | 6-1 |

|           | 6.1.1  | General                                               | 6-1 |

|           | 6.1.2  | Power Amplifier                                       | 6-1 |

|           | 6.1.3  | Antenna Switch                                        | 6-2 |

|           | 6.1.4  | Harmonic Filter                                       | 6-2 |

|           | 6.1.5  | Antenna Matching Network                              | 6-2 |

|           | 6.1.6  | Power Control Integrated Circuit (PCIC)               | 6-2 |

| 6.2       | Receiv | ver (for all models except those with PCB 8486473Z04) | 6-3 |

|           | 6.2.1  | Receiver Front-End                                    | 6-3 |

|           | 6.2.2  | Receiver Back-End                                     | 6-4 |

|           | 6.2.3  | Automatic Gain Control Circuit                        | 6-4 |

| 6.3       | Receiv | ver (for models with PCB 8486473Z04)                  | 6-5 |

|           | 6.3.1  | Receiver Front-End                                    | 6-6 |

|           | 6.3.2  | Receiver Back-End                                     | 6-6 |

|       | 6.3.3 Automatic Gain Control Circuit                   | 6-7  |

|-------|--------------------------------------------------------|------|

| 6.4   | Frequency Generation Circuitry                         | 6-8  |

| 6.5   | Synthesizer                                            | 6-9  |

| 6.6   | Voltage-Controlled Oscillator (VCO)                    | 6-10 |

| Chapt | ter 7 Low Band, 800 MHz, PassPort & 900 MHz            |      |

|       | Theory of Operation                                    | 7-1  |

| 7.1   | Introduction                                           | 7-1  |

| 7.2   | Low Band Transmitter                                   |      |

|       | 7.2.1 Power Amplifier (PA)                             |      |

|       | 7.2.2 Antenna Switch                                   |      |

|       | 7.2.3 Harmonic Filter                                  |      |

|       | 7.2.4 Antenna Matching Transformer                     |      |

|       | 7.2.5 Power Control Integrated Circuit (PCIC)          |      |

|       | 7.2.6 Temperature Cut Back Circuit                     |      |

|       | 7.2.7 Electrostatic Discharge (ESD) Protection Circuit |      |

| 7.3   | Low Band Receiver                                      |      |

|       | 7.3.1 Receiver Front-End                               |      |

|       | 7.3.2 Receiver Back-End                                |      |

|       | 7.3.3 Automatic Gain Control (AGC)                     |      |

|       | 7.3.4 Frequency Generation Circuit                     |      |

| 7.4   | Synthesizer                                            |      |

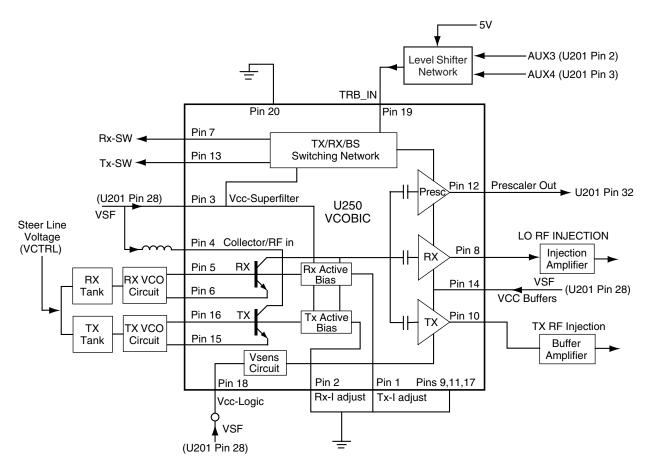

| 7.5   | Voltage Control Oscillators (VCO)                      | 7-6  |

|       | 7.5.1 Receive VCO                                      |      |

|       | 7.5.2 Transmit VCO                                     | 7-6  |

|       | 7.5.3 Buffer                                           | 7-6  |

|       | 7.5.4 Diplexer/Output Filters                          | 7-7  |

|       | 7.5.5 Prescalar Feedback                               | 7-7  |

| 7.6   | 800 MHz Transmitter                                    | 7-7  |

|       | 7.6.1 Power Amplifier                                  | 7-7  |

|       | 7.6.2 Antenna Switch                                   | 7-8  |

|       | 7.6.3 Harmonic Filter                                  | 7-8  |

|       | 7.6.4 Power Control Integrated Circuit (PCIC)          | 7-8  |

| 7.7   | 800 MHz Receiver                                       | 7-9  |

|       | 7.7.1 Receiver Front-End                               | 7-9  |

|       | 7.7.2 Receiver Back-End                                | 7-10 |

|       | 7.7.3 Automatic Gain Control Circuit                   | 7-10 |

|       | 7.7.4 Frequency Generation Circuit                     | 7-11 |

| 7.8   | Synthesizer                                            | 7-12 |

|       | 7.8.1 Voltage Control Oscillator (VCO)                 | 7-13 |

| 7.9   | Trunked Radio Systems                                  | 7-14 |

|       | 7.9.1 Privacy Plus Trunked Systems                     |      |

|       | 7.9.2 LTR™ Trunked Systems                             | 7-14 |

|       | 7.9.3 MPT Trunked Systems                              | 7-14 |

|       | 7.9.4 PassPort™ Trunked Systems                        | 7-15 |

|       | 7.9.4.1 Power Supplies                                 | 7-15 |

vi Table of Contents

|   |       | 7.9     | 4.2 Microcontroller (MCU)                                                                   | 7-15 |

|---|-------|---------|---------------------------------------------------------------------------------------------|------|

|   |       | 7.9     | 4.3 Low Speed Data Filter                                                                   | 7-15 |

|   |       | 7.9     | 4.4 Keyboard Circuit                                                                        | 7-15 |

|   |       | 7.9     | 3                                                                                           |      |

|   |       | _       | 4.6 Voice Storage                                                                           |      |

|   | 7.10  |         | Iz Transmitter                                                                              |      |

|   |       |         | Power Amplifier                                                                             |      |

|   |       |         | Antenna Switch                                                                              |      |

|   |       |         | Harmonic Filter                                                                             |      |

|   |       |         | Power Control Integrated Circuit (PCIC)                                                     |      |

|   | 7.11  |         | Iz Receiver                                                                                 |      |

|   |       |         | Receiver Front-End                                                                          |      |

|   |       |         | Receiver Back-End                                                                           |      |

|   |       | 7.11.3  | Hear Clear IC                                                                               |      |

|   |       |         | 1.3.1 Receive Path for Radios with Hear Clear                                               |      |

|   |       |         | 1.3.2 Hear Clear Routing of Data/Signaling                                                  |      |

|   |       |         | Automatic Gain Control Circuit                                                              |      |

|   |       | -       | ncy Generation Circuitry                                                                    |      |

|   |       |         | Iz Synthesizer                                                                              |      |

|   | 7.14  | 900 MF  | Iz Voltage Control Oscillator (VCO)                                                         | 7-24 |

| С | hapte | er 8    | Maintenance                                                                                 | 8-1  |

|   | 8.1   | Introdu | ction                                                                                       | 8-1  |

|   | 8.2   |         | tive Maintenance                                                                            |      |

|   | 8.3   |         | ion                                                                                         |      |

|   | 0.0   | 8.3.1   | Cleaning                                                                                    |      |

|   | 8.4   |         | andling of CMOS and LDMOS                                                                   |      |

|   | 8.5   |         | Repair Procedures and Techniques                                                            |      |

|   | 8.6   |         | mended Test Tools                                                                           |      |

|   | 8.7   |         | ing the Circuit Board Fuse                                                                  |      |

|   | 8.8   | •       | ing and Reinstalling the Circuit Board                                                      |      |

|   | 8.9   |         | Up Self-Test Error Codes                                                                    |      |

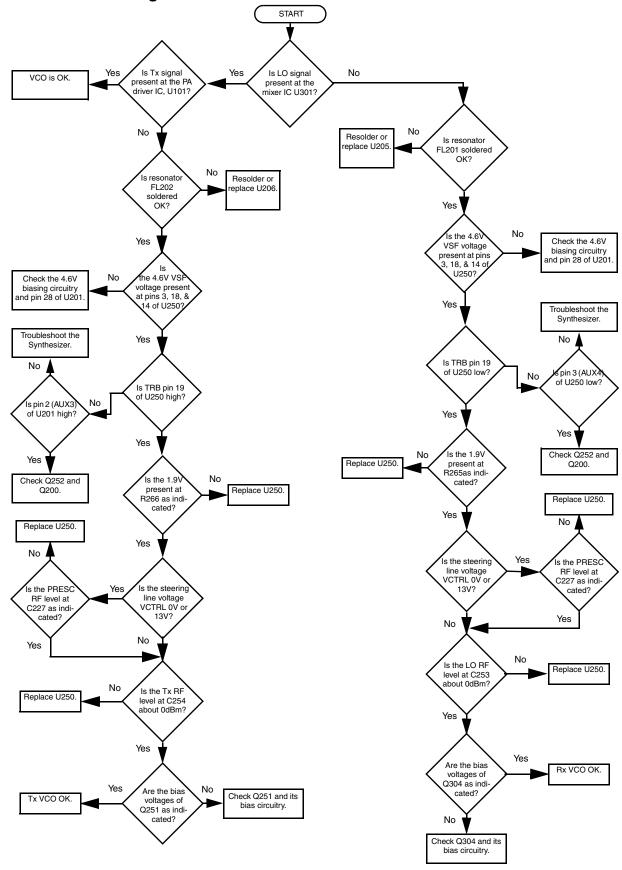

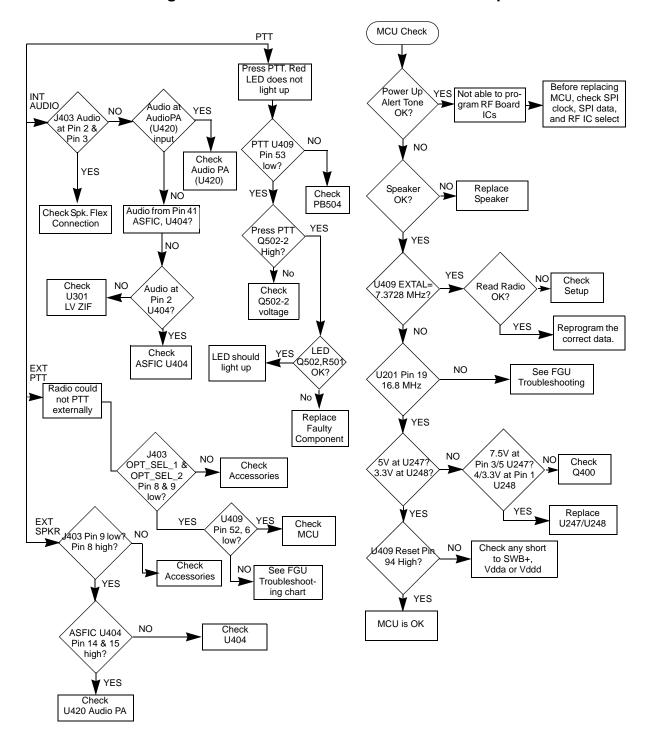

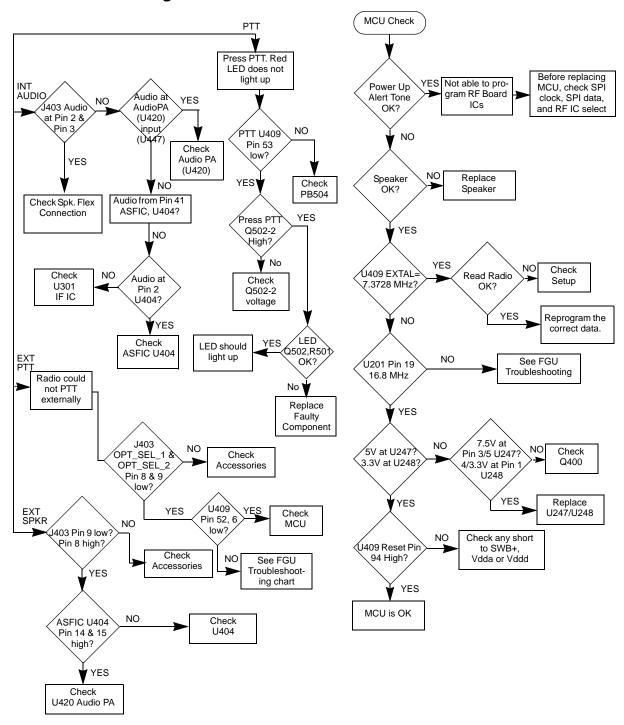

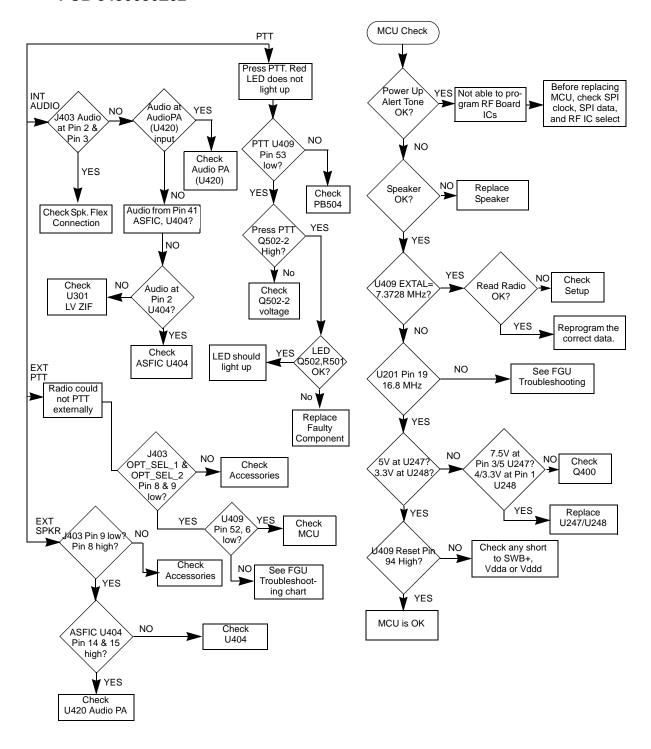

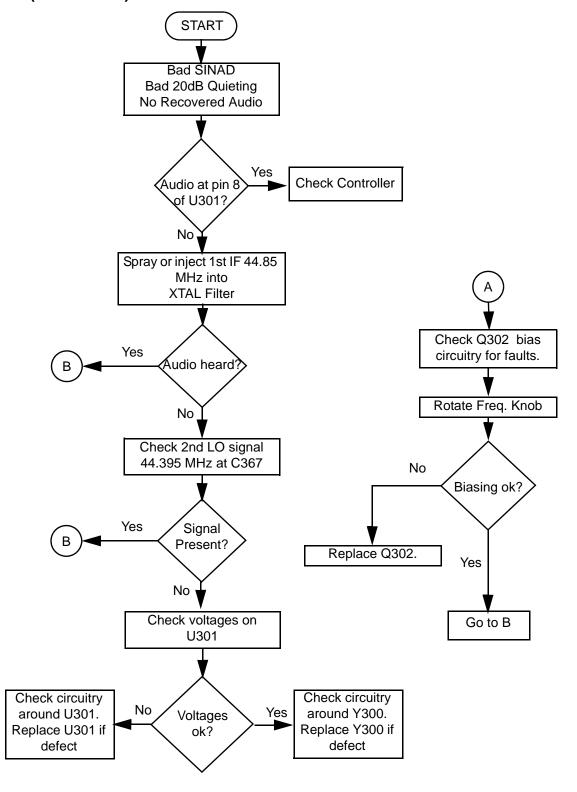

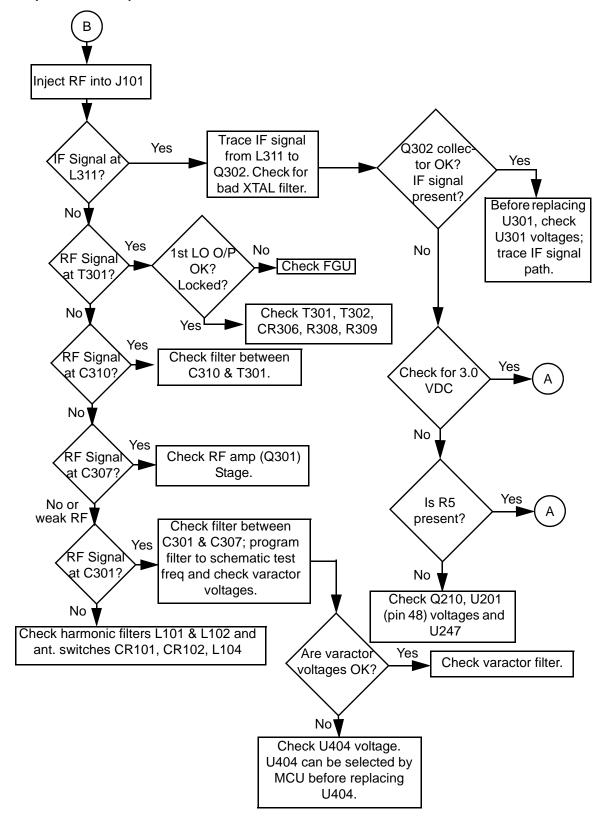

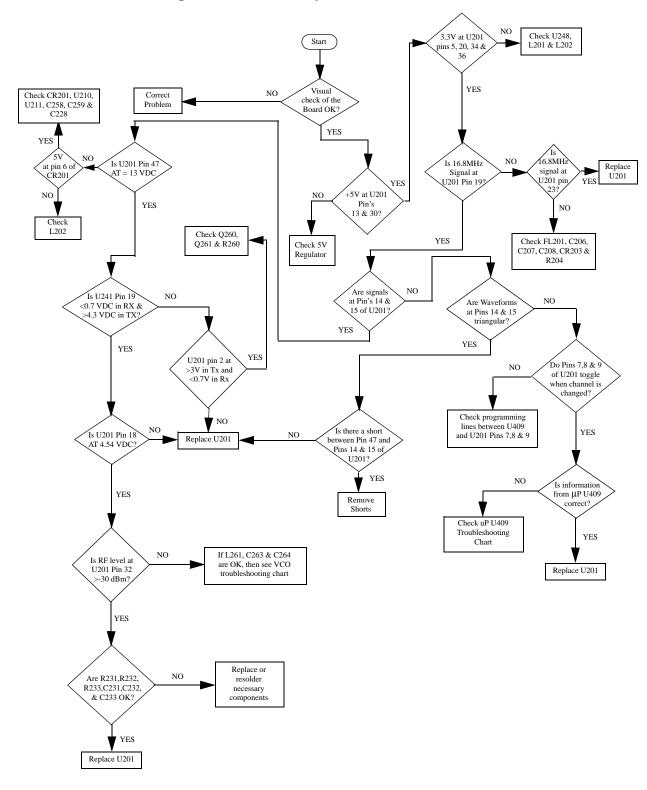

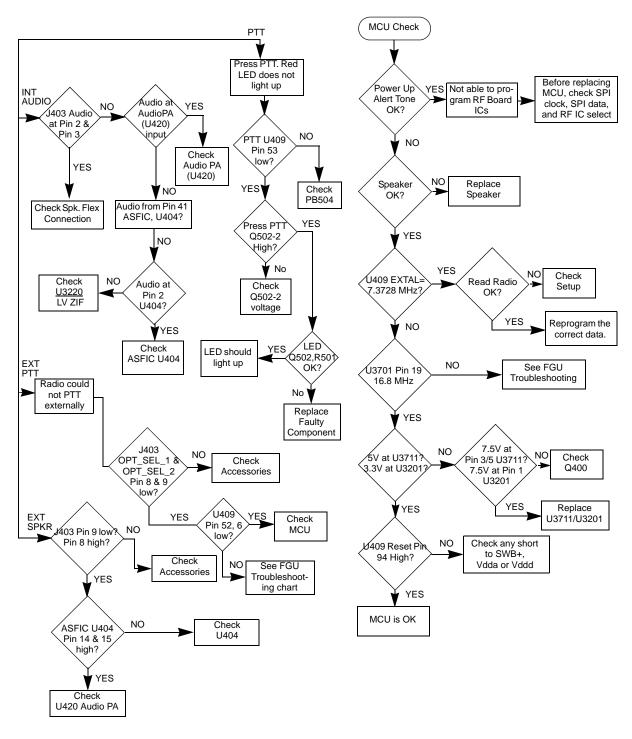

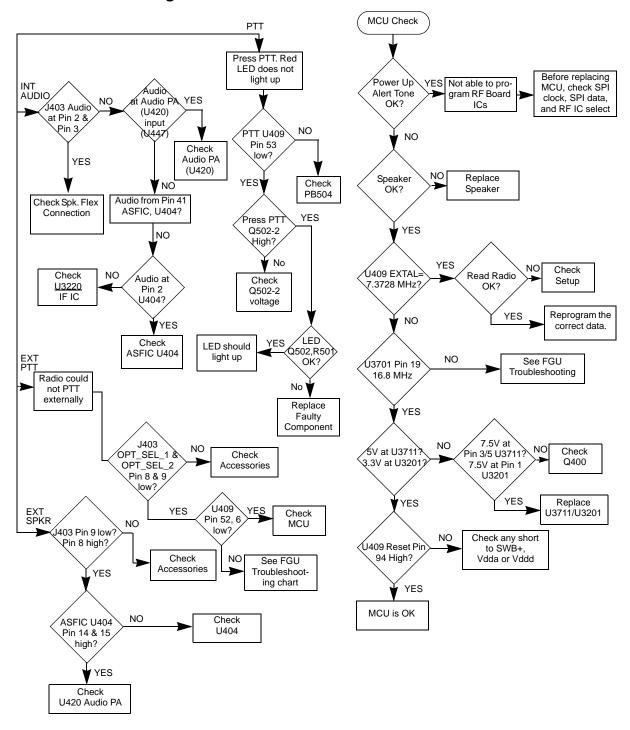

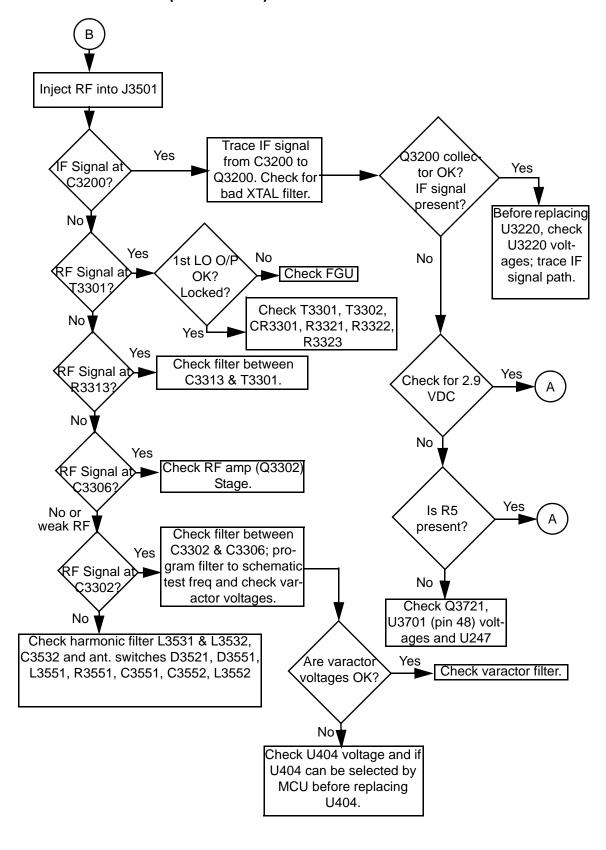

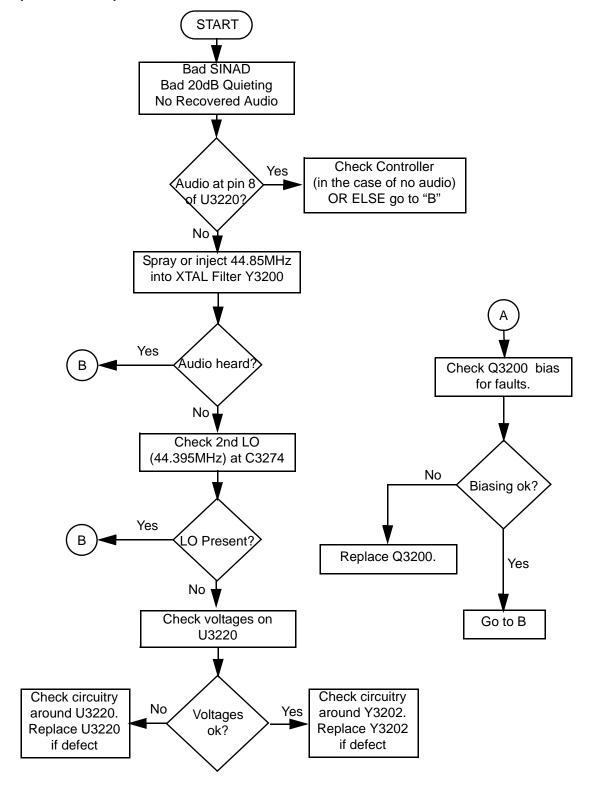

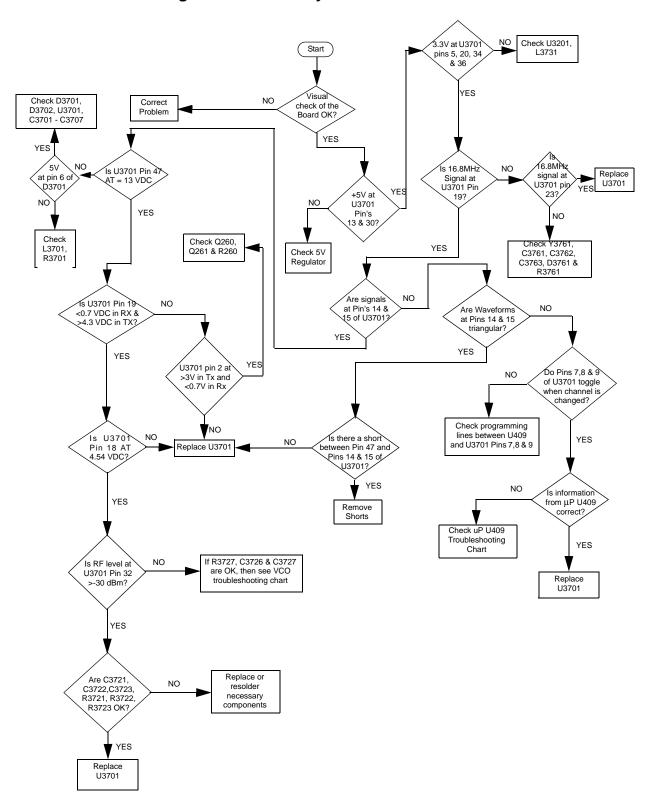

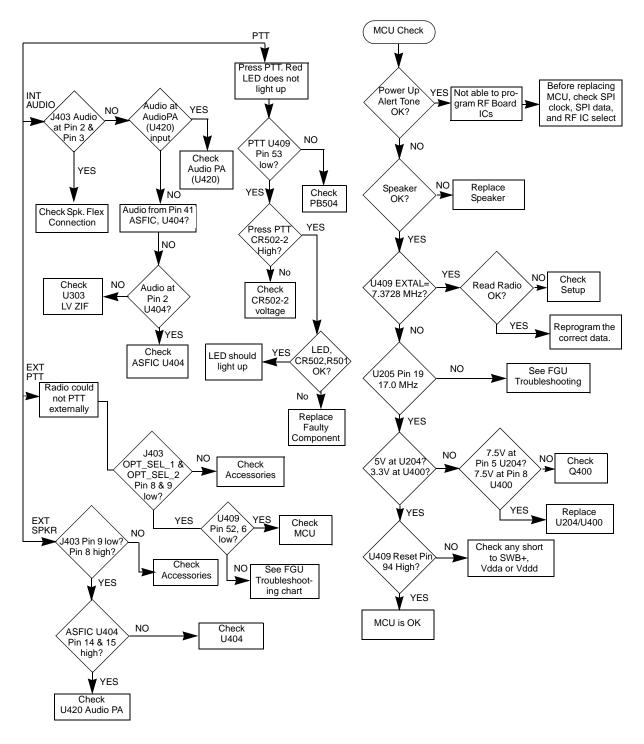

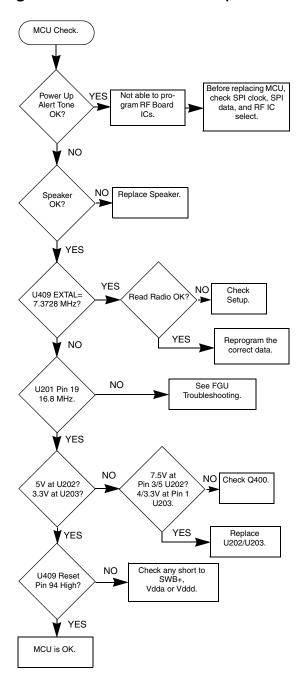

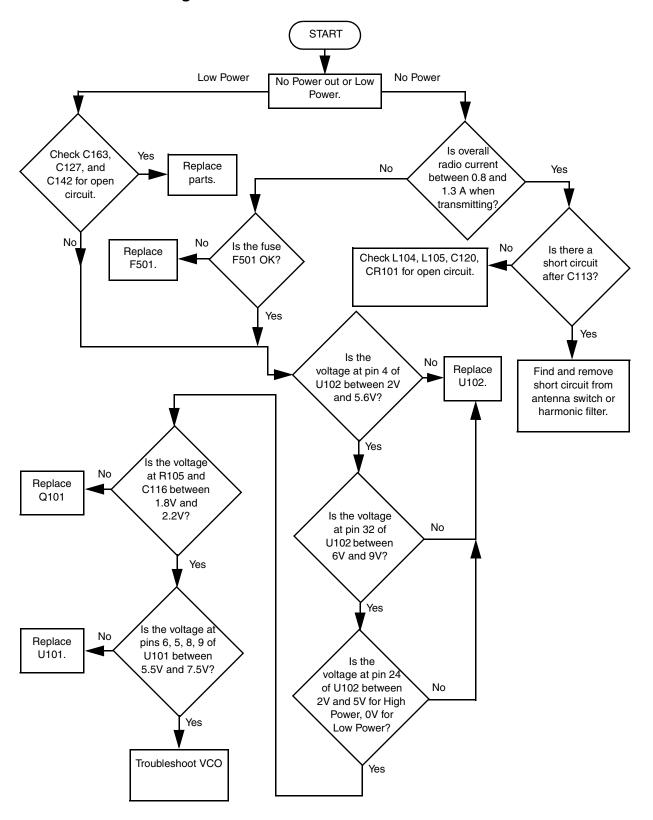

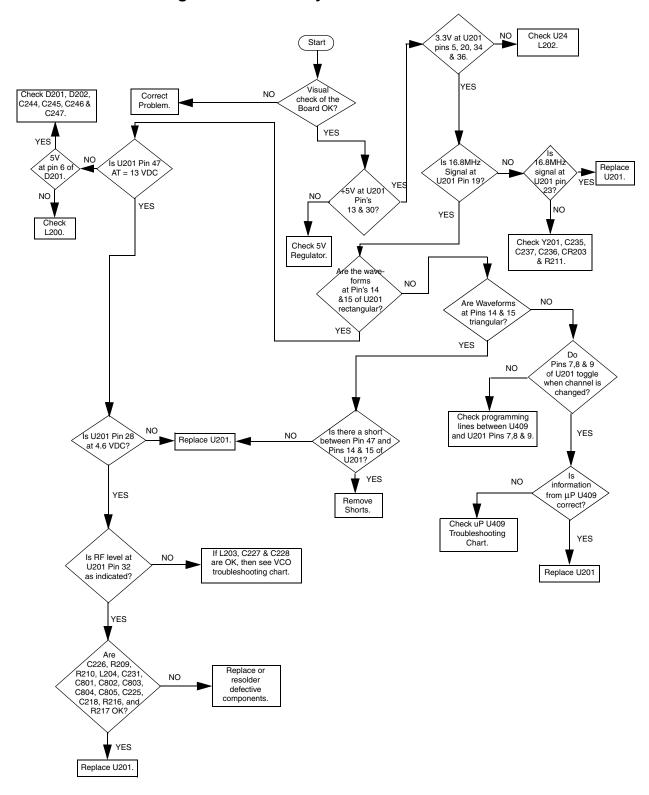

|   |       |         | and 1 Troubleshooting Charts                                                                |      |

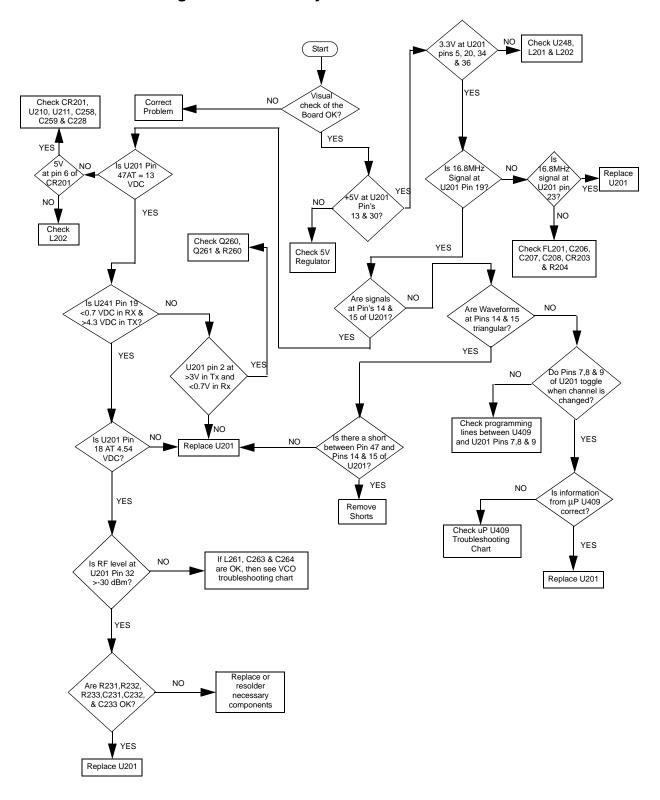

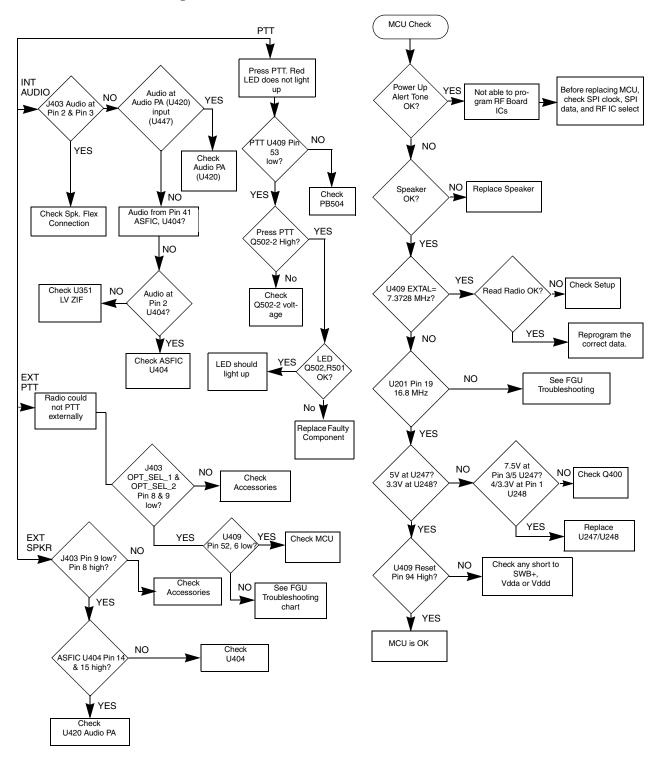

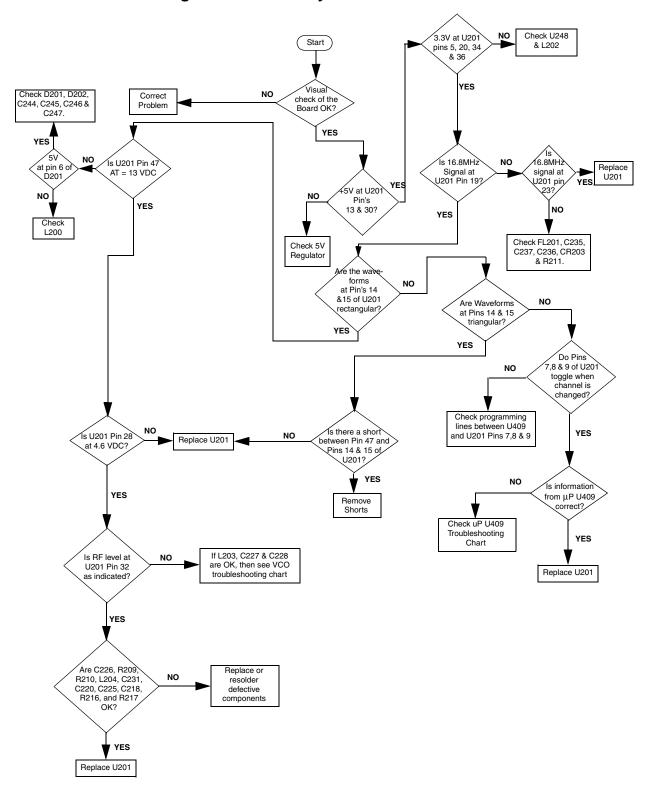

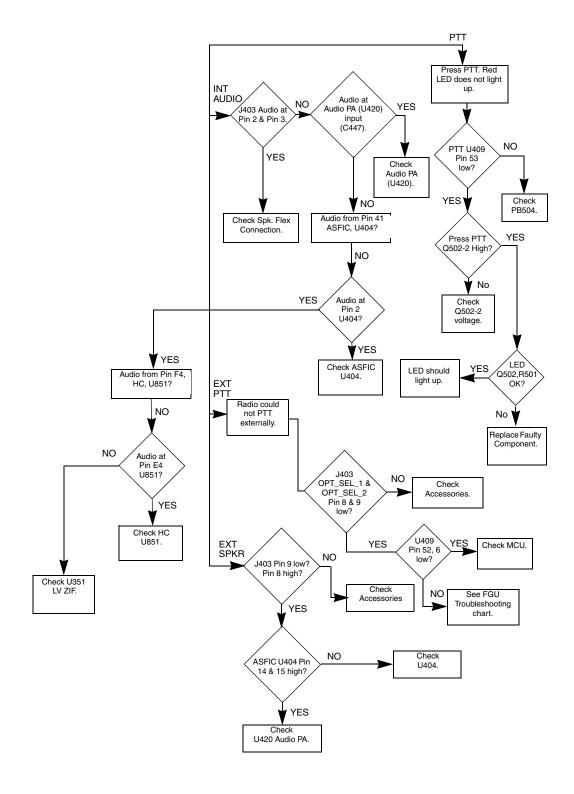

|   |       | 8.10.1  | Troubleshooting Flow Chart for Controller for all models except PCB 8486458Z03              |      |

|   |       | 8.10.2  | Troubleshooting Flow Chart for Controller for models with                                   |      |

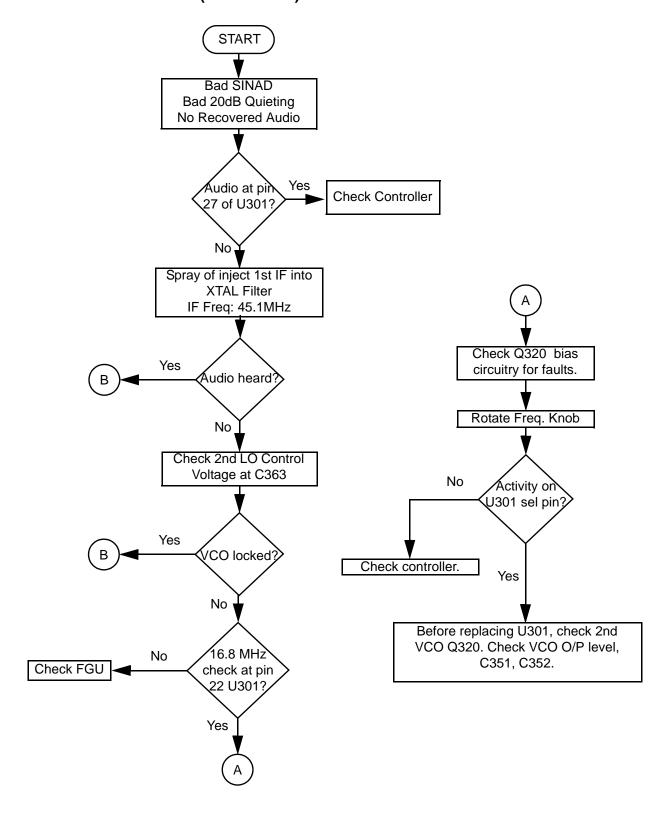

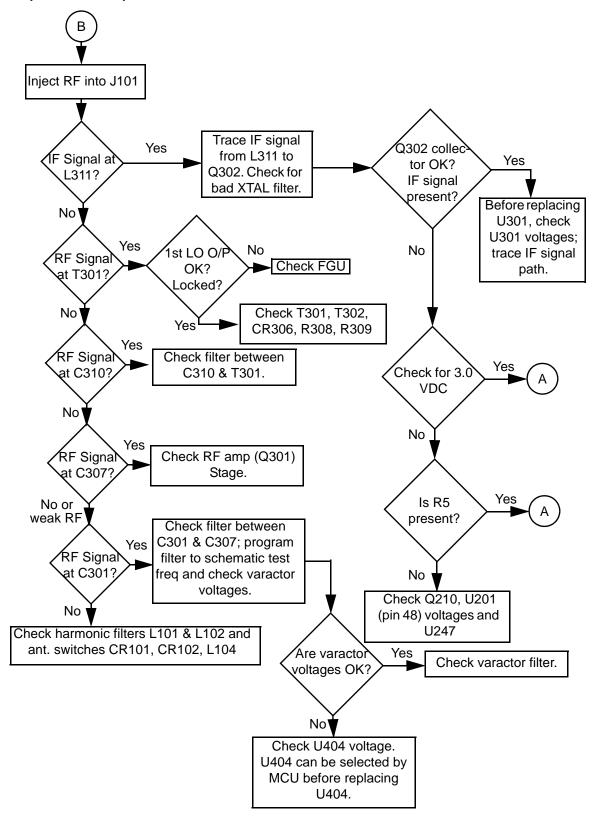

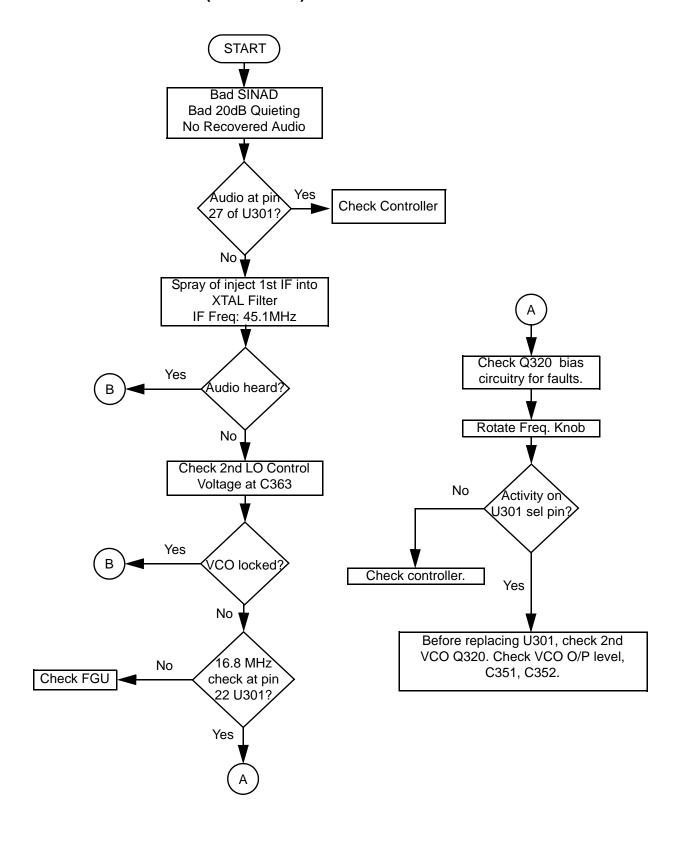

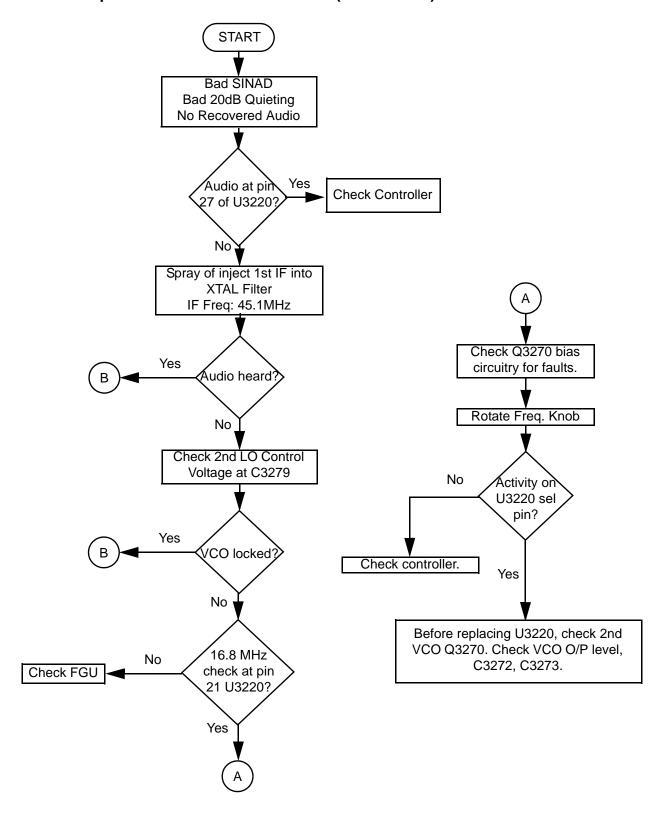

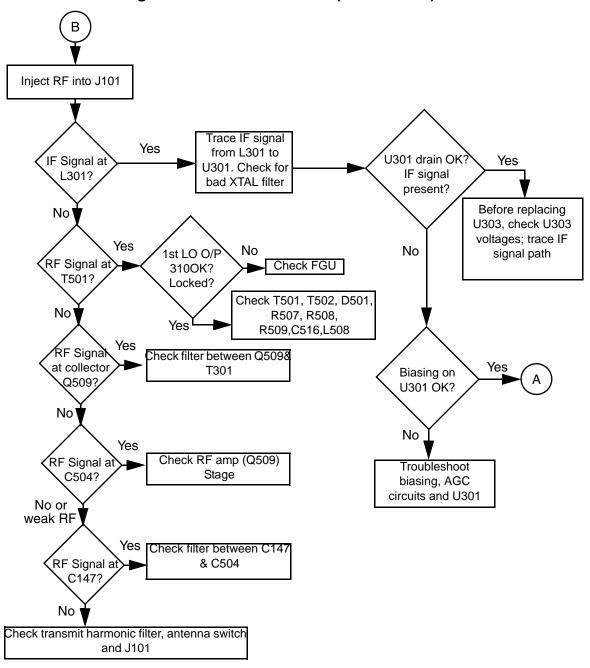

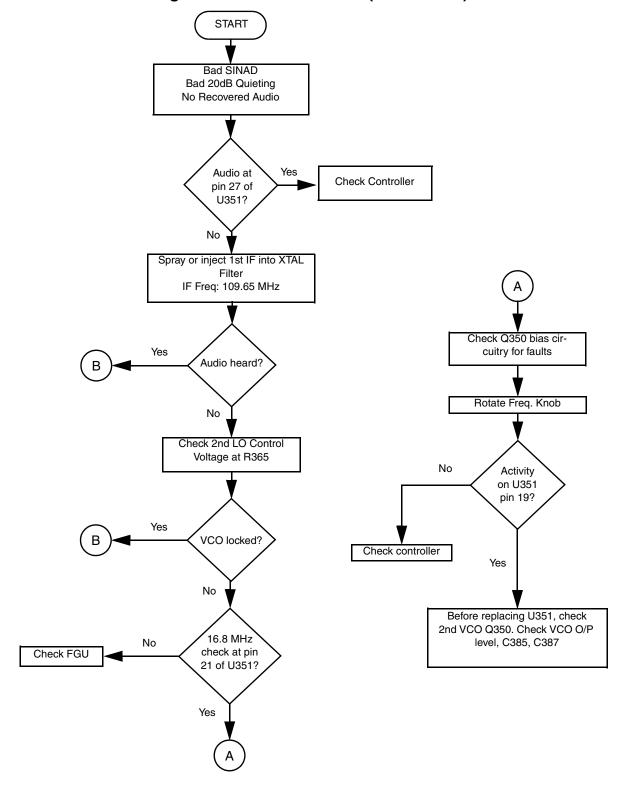

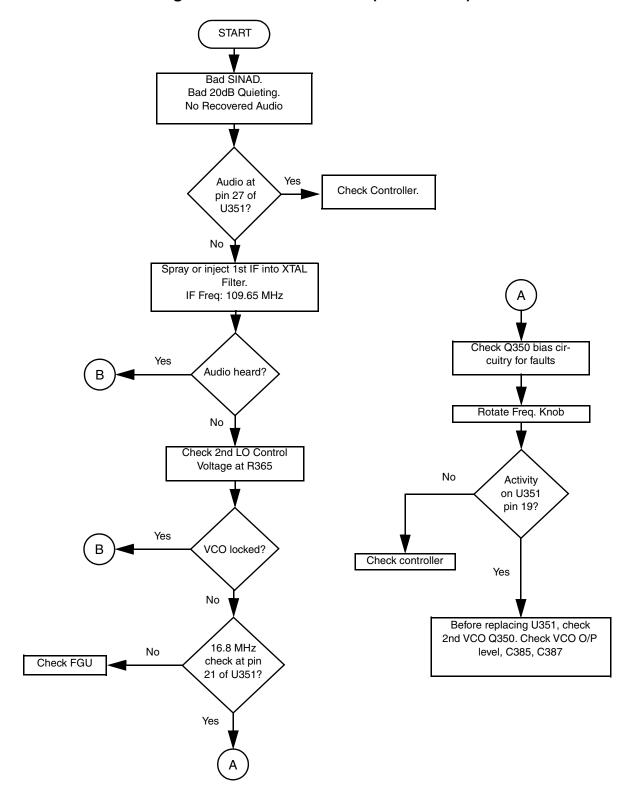

|   |       | 8.10.3  | PCB 8486458Z03  Troubleshooting Flow Chart for Receiver for all models except               |      |

|   |       |         | PCB 8486458Z03 (Sheet 1 of 2)                                                               | 8-11 |

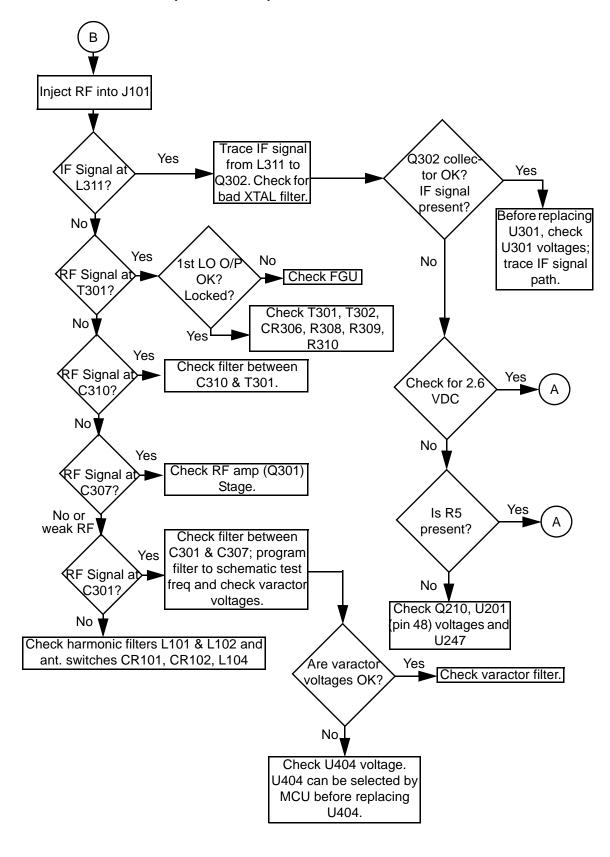

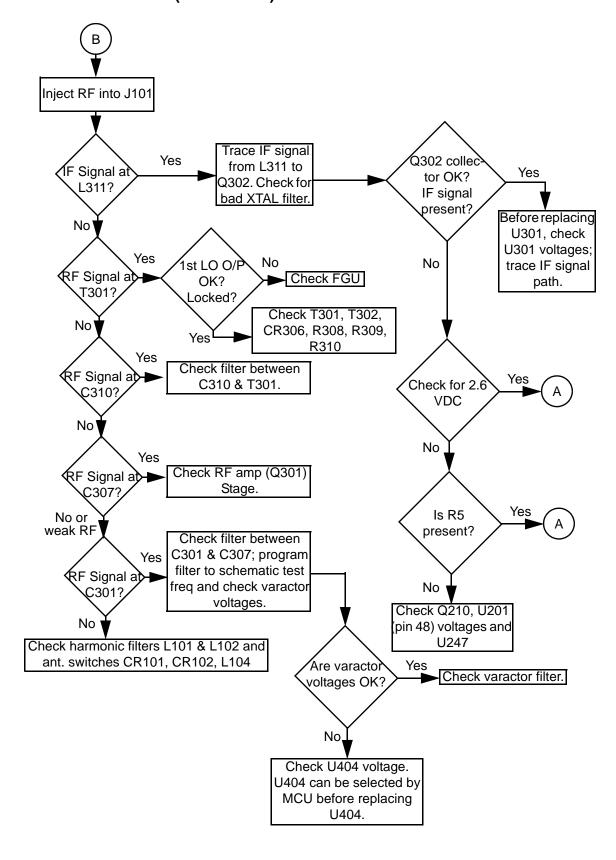

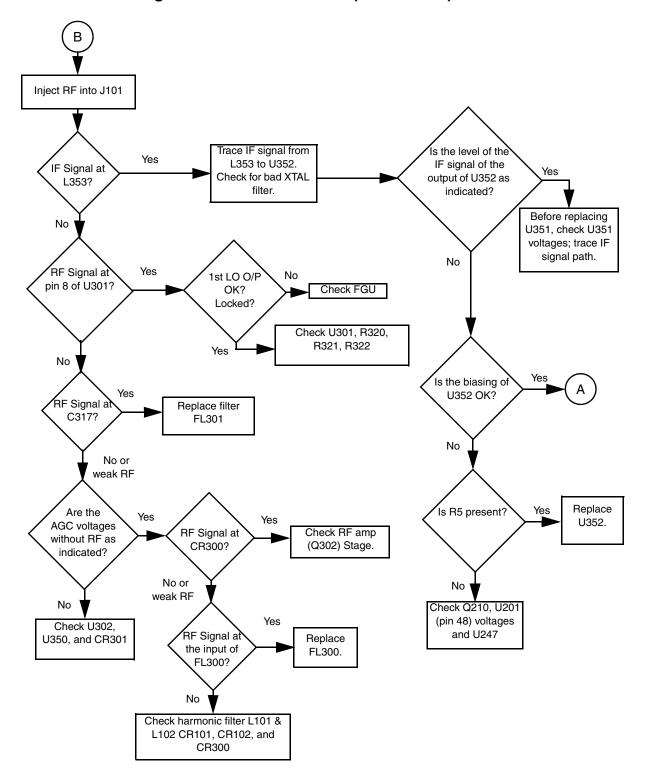

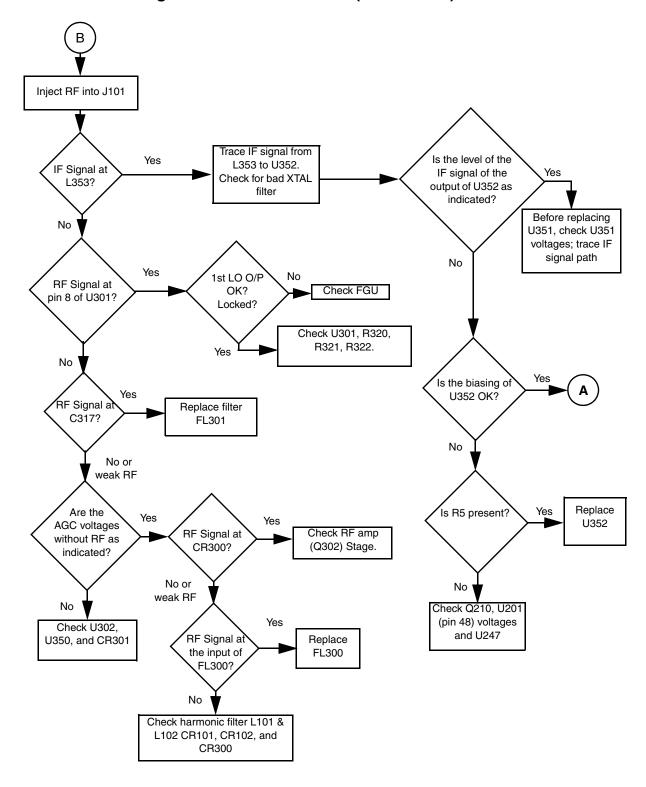

|   |       | 8.10.4  | Troubleshooting Flow Chart for Receiver for all models except PCB 8486458Z03 (Sheet 2 of 2) | 8-12 |

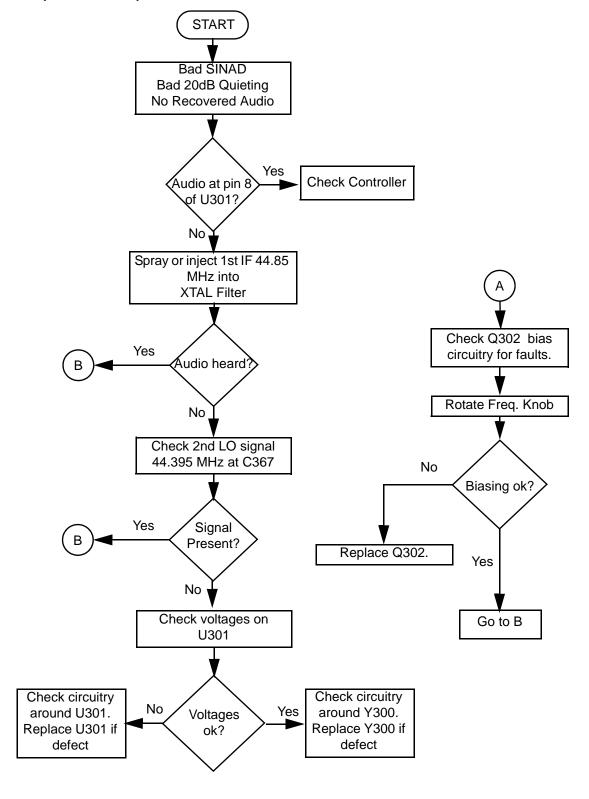

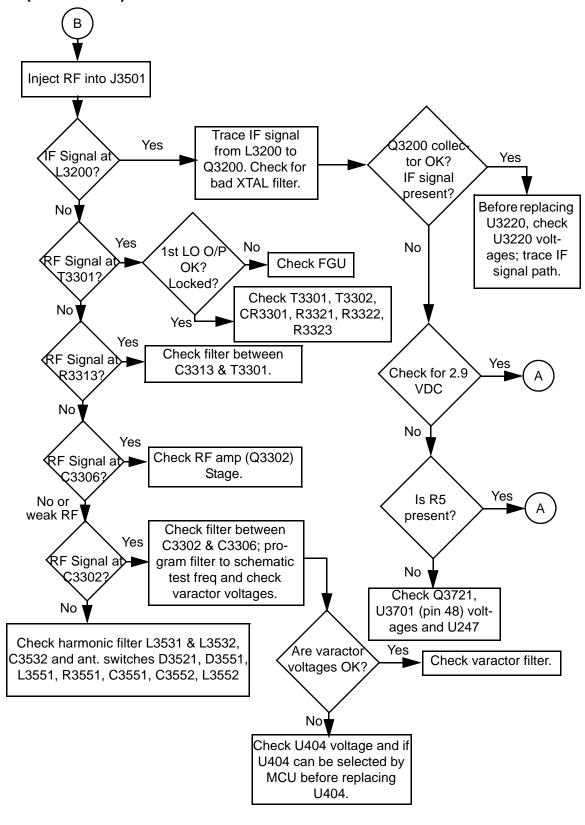

|   |       | 8.10.5  | Troubleshooting Flow Chart for Receiver, for models with PCB 8486458Z03 (Sheet 1 of 2)      | 8-13 |

|   |       | 8.10.6  | Troubleshooting Flow Chart for Receiver, for models with                                    |      |

|   |       | 30.0    | PCB 8486458Z03 (Sheet 2 of 2)                                                               | 8-14 |

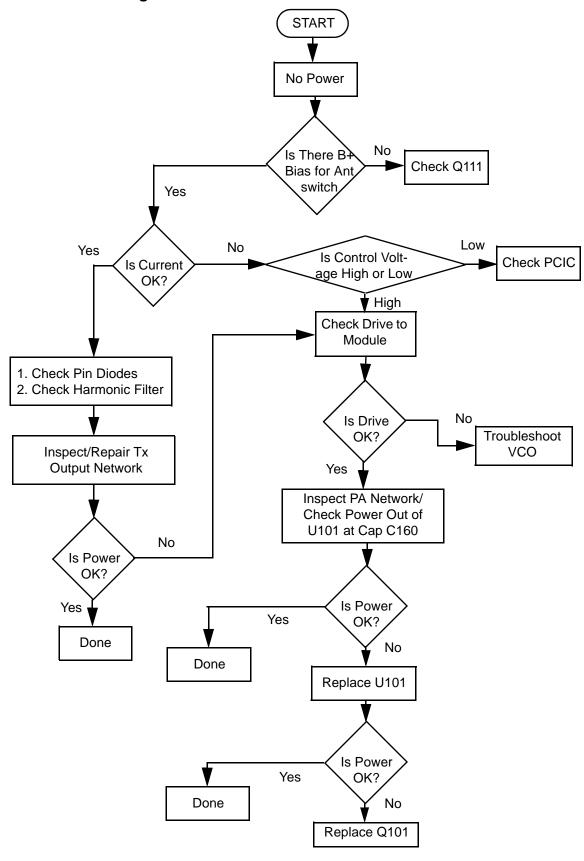

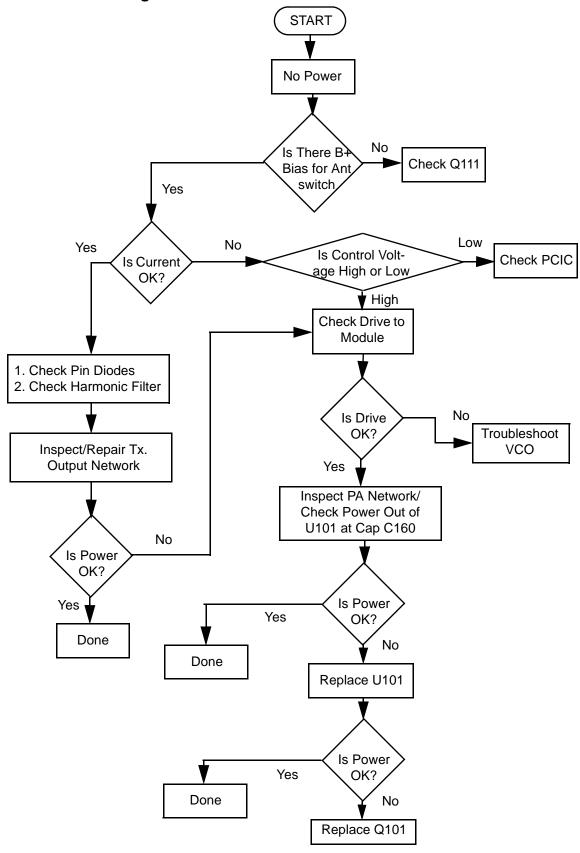

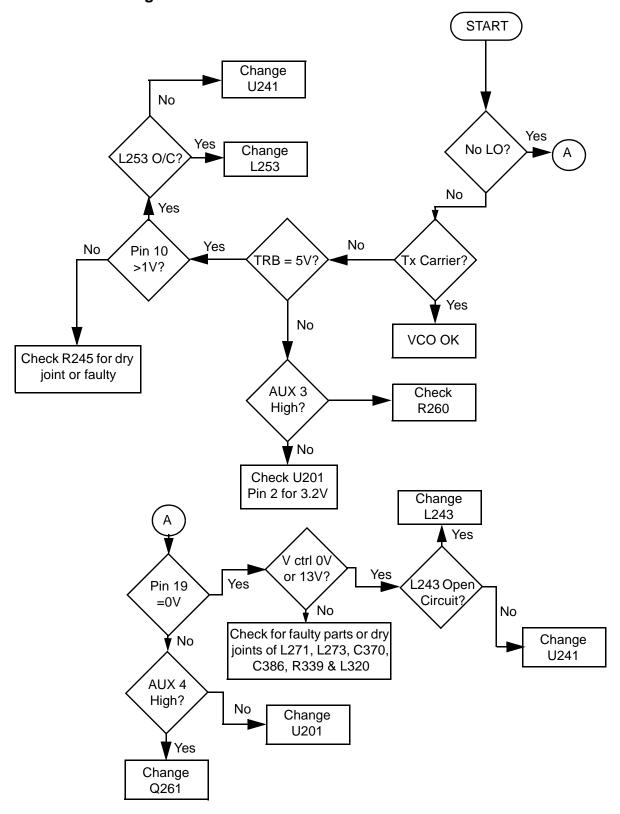

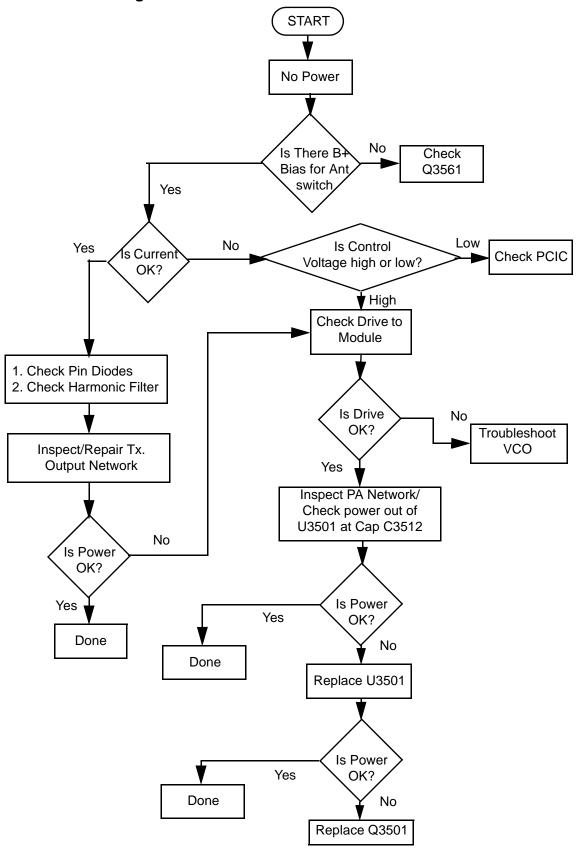

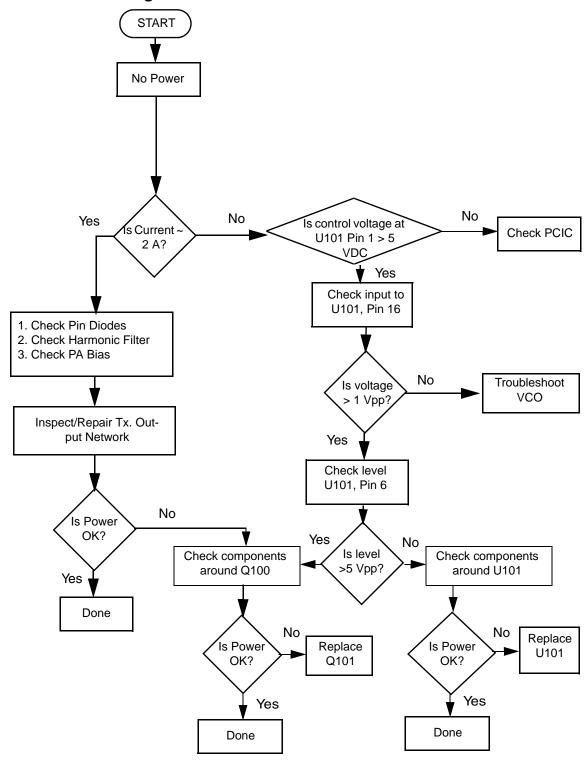

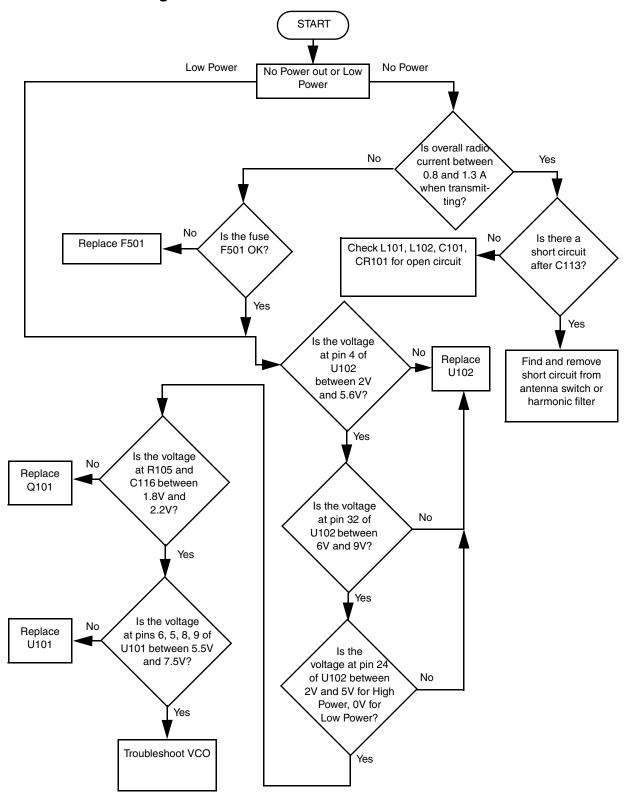

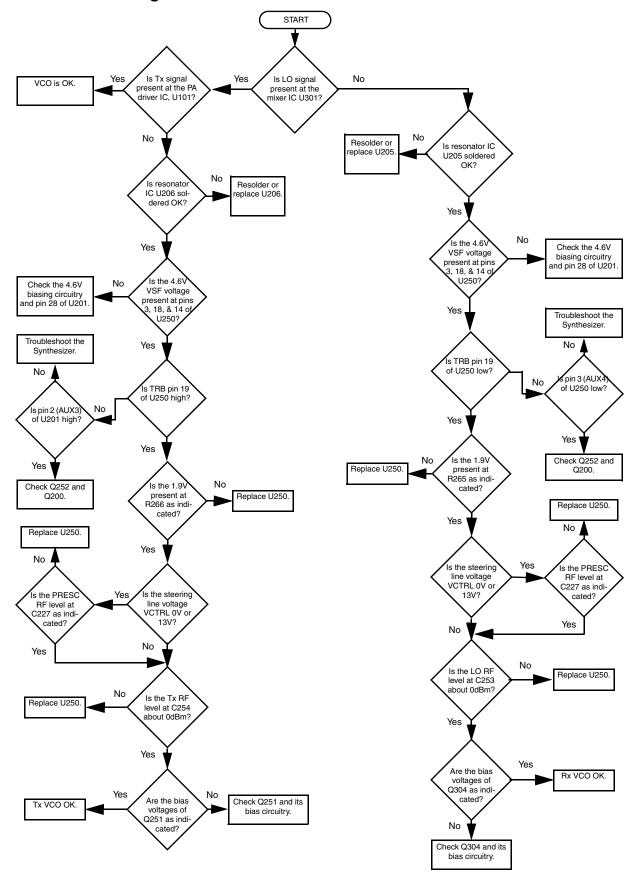

|   |       | 8.10.7  | Troubleshooting Flow Chart for Transmitter                                                  |      |

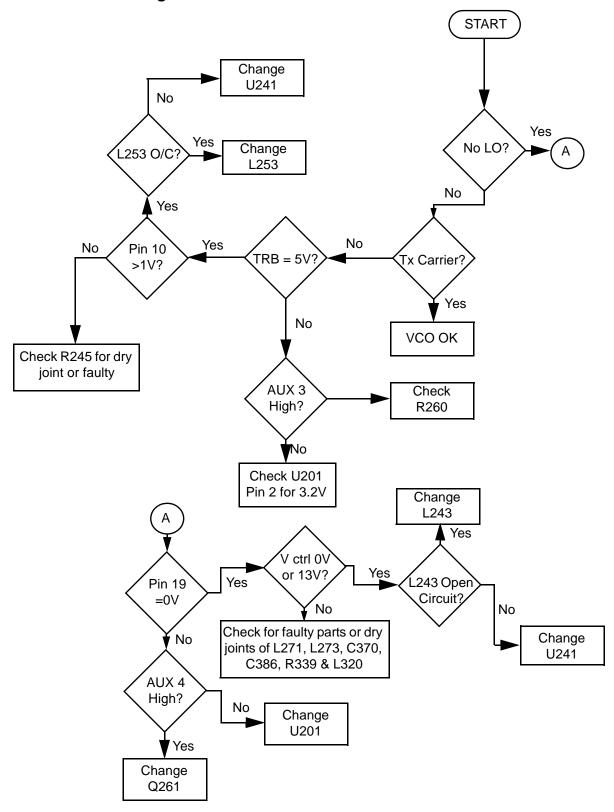

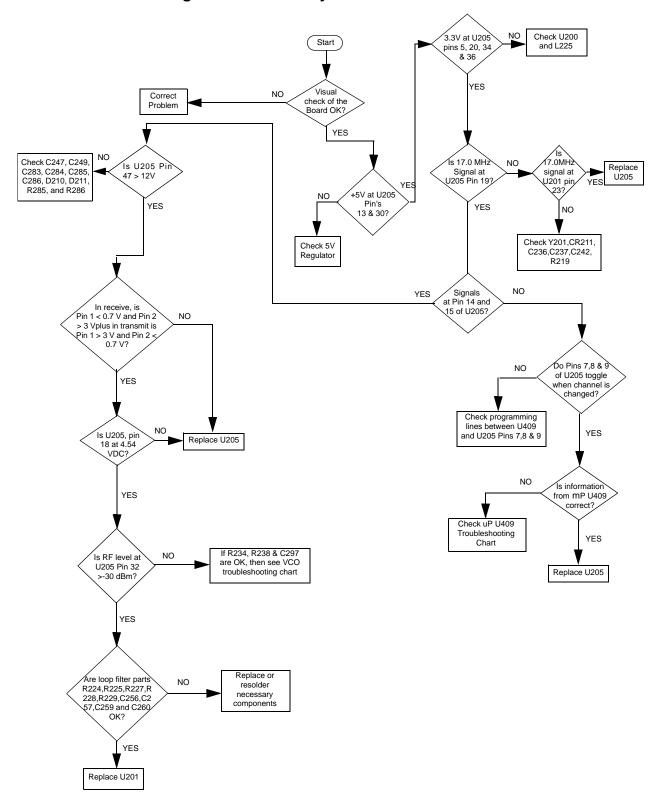

|   |       |         | Troubleshooting Flow Chart for Synthesizer                                                  |      |

|   |       |         |                                                                                             |      |

Table of Contents vii

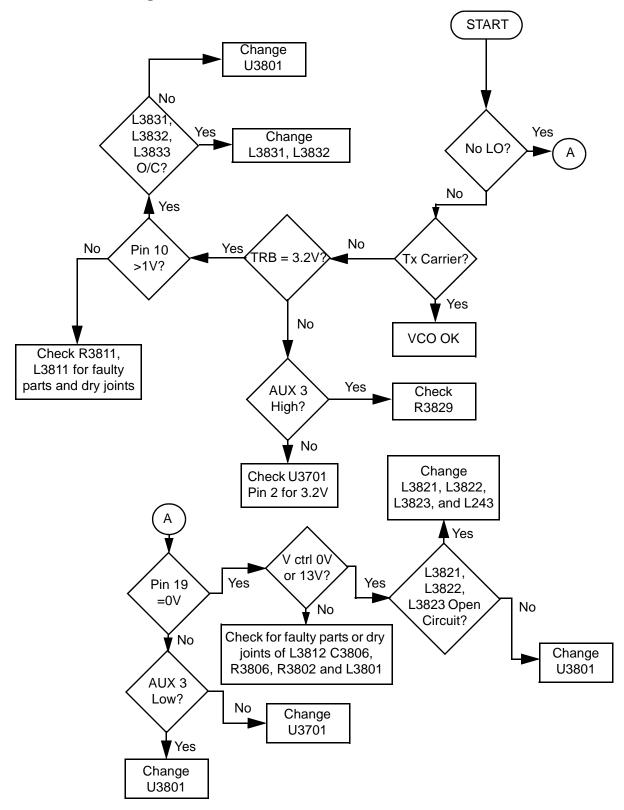

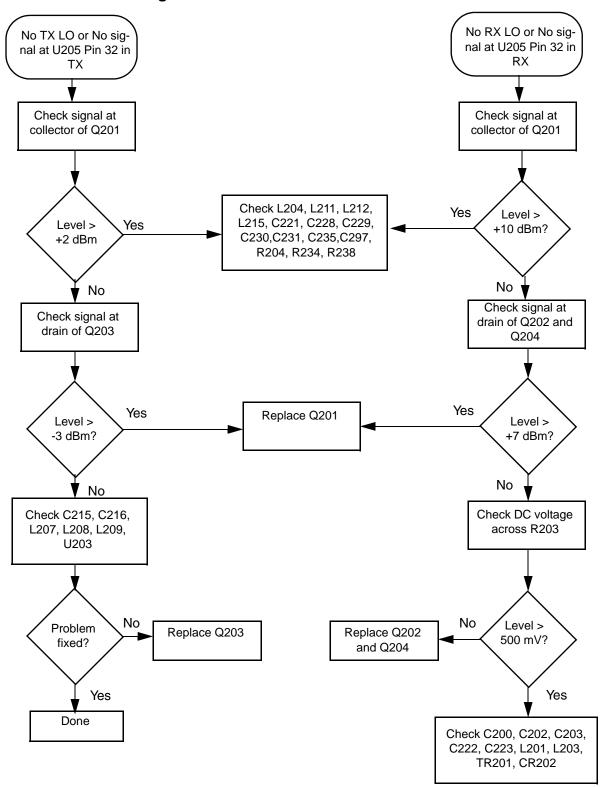

|       | 8.10.9 | Troubleshooting Flow Chart for VCO                                                                      | 8-17 |

|-------|--------|---------------------------------------------------------------------------------------------------------|------|

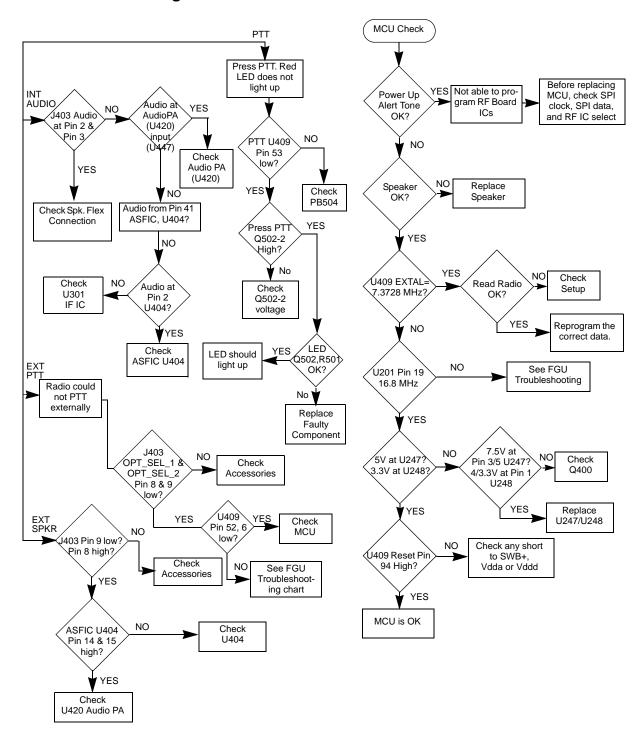

| 8.11  |        | and 2 Troubleshooting Charts                                                                            |      |

|       |        | Troubleshooting Flow Chart for Controller for all models                                                |      |

|       |        | except those with PCB 8486686Z02                                                                        | 8-18 |

|       | 8.11.2 | Troubleshooting Flow Chart for Controller for models with                                               |      |

|       |        | PCB 8486686Z02                                                                                          | 8-19 |

|       | 8.11.3 | Troubleshooting Flow Chart for Receiver, for all models                                                 |      |

|       |        | except those with PCB 8486686Z02 (Sheet 1 of 2)                                                         | 8-20 |

|       | 8.11.4 |                                                                                                         |      |

|       |        | except those with PCB 8486686Z02 (Sheet 2 of 2)                                                         | 8-21 |

|       | 8.11.5 | Troubleshooting Flow Chart for Receiver, for models with                                                |      |

|       |        | PCB 8486686Z02 (Sheet 1 of 2)                                                                           | 8-22 |

|       | 8.11.6 | Troubleshooting Flow Chart for Receiver, for models with                                                |      |

|       |        | PCB 8486686Z02 (Sheet 2 of 2)                                                                           |      |

|       | 8.11.7 | 9                                                                                                       |      |

|       |        | Troubleshooting Flow Chart for Synthesizer                                                              |      |

|       |        | Troubleshooting Flow Chart for VCO                                                                      |      |

| 8.12  |        | oubleshooting Charts                                                                                    | 8-27 |

|       | 8.12.1 | Troubleshooting Flow Chart for Controller for all models                                                |      |

|       |        | except those with PCB 8486473Z04                                                                        | 8-27 |

|       | 8.12.2 | 3                                                                                                       |      |

|       | 0.40.0 | PCB 8486473Z04                                                                                          | 8-28 |

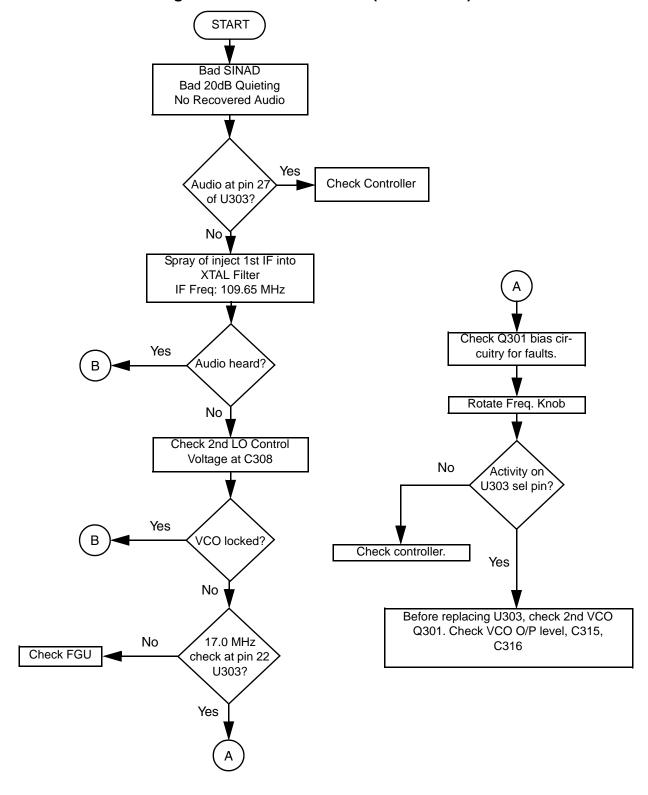

|       | 8.12.3 | Troubleshooting Flow Chart for Receiver, for all models                                                 | 0.00 |

|       | 0.40.4 | except those with PCB 8486473Z04 (Sheet 1 of 2)                                                         | 8-29 |

|       | 8.12.4 | Troubleshooting Flow Chart for Receiver, for all models except those with PCB 8486473Z04 (Sheet 2 of 2) | 9 20 |

|       | 8.12.5 | Troubleshooting Flow Chart for Receiver for models with                                                 | 6-30 |

|       | 0.12.3 | PCB 8486473Z04 (Sheet 1 of 2)                                                                           | 8-31 |

|       | 8.12.6 | Troubleshooting Flow Chart for Receiver for models with                                                 | 0-31 |

|       | 0.12.0 | PCB 8486473Z04 (Sheet 2 of 2)                                                                           | 8-32 |

|       | 8.12.7 | ·                                                                                                       |      |

|       |        | Troubleshooting Flow Chart for Synthesizer                                                              |      |

|       |        | Troubleshooting Flow Chart for VCO                                                                      |      |

| 8 13  |        | and Troubleshooting Charts                                                                              |      |

| 0.10  |        | Troubleshooting Flow Chart for Controller                                                               |      |

|       | 8.13.2 |                                                                                                         |      |

|       | 8.13.3 |                                                                                                         |      |

|       |        | Troubleshooting Flow Chart for Transmitter                                                              |      |

|       | 8.13.5 | Troubleshooting Flow Chart for Synthesizer                                                              |      |

|       |        | Troubleshooting Flow Chart for VCO                                                                      |      |

| 8 14  |        | Hz Troubleshooting Charts                                                                               |      |

| J. 17 | 8.14.1 |                                                                                                         |      |

|       | 8.14.2 |                                                                                                         |      |

|       |        | Troubleshooting Flow Chart for Receiver (Sheet 2 of 2)                                                  |      |

|       | 8.14.4 | ,                                                                                                       |      |

|       | 8.14.5 | •                                                                                                       |      |

|       |        | Troubleshooting Flow Chart for VCO                                                                      |      |

|       | 0.14.0 | TIOUDIESTIDUTING FIOW CHAILIUL VOO                                                                      | 0-4/ |

viii Table of Contents

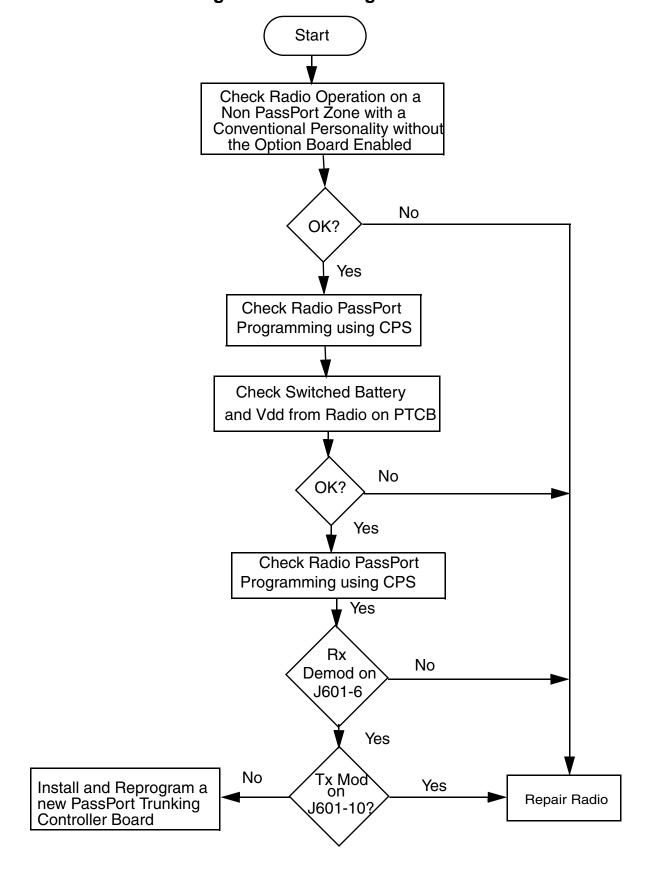

|    | 8.15 | PassPort Trunking Troubleshooting Chart                                    | 8-48  |

|----|------|----------------------------------------------------------------------------|-------|

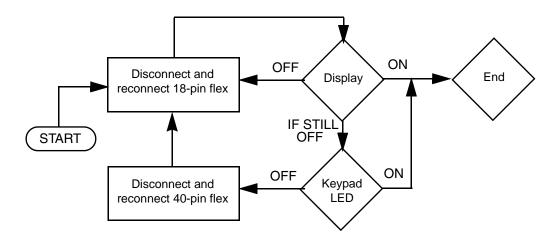

|    | 8.16 | Keypad Troubleshooting Chart                                               | 8-49  |

|    | 8.17 | 900 MHz Troubleshooting Charts                                             | 8-50  |

|    |      | 8.17.1 Troubleshooting Flow Chart for Controller (Sheet 1 of 2)            | 8-50  |

|    |      | 8.17.2 Troubleshooting Flow Chart for Controller (Sheet 2 of 2)            | 8-51  |

|    |      | 8.17.3 Troubleshooting Flow Chart for Receiver (Sheet 1 of 2)              | 8-52  |

|    |      | 8.17.4 Troubleshooting Flow Chart for Receiver (Sheet 2 of 2)              | 8-53  |

|    |      | 8.17.5 Troubleshooting Flow Chart for Transmitter                          |       |

|    |      | 8.17.6 Troubleshooting Flow Chart for Synthesizer                          | 8-55  |

|    |      | 8.17.7 Troubleshooting Flow Chart for VCO                                  | 8-56  |

| Ch | apte | er 9 Schematic Diagrams, Overlays, and Parts Lists                         | 9-1   |

|    | 9.1  | Introduction                                                               | 9-1   |

|    |      | 9.1.1 Notes For All Schematics and Circuit Boards                          | 9-1   |

|    | 9.2  | Flex Layout                                                                | 9-2   |

|    |      | 9.2.1 Keypad-Controller Interconnect Flex Schematic                        | 9-3   |

|    |      | 9.2.2 Keypad-Controller Interconnect Flex Parts List                       | 9-3   |

|    |      | 9.2.3 Universal Flex Connector                                             | 9-4   |

|    |      | 9.2.4 Universal Connector Flex Schematic                                   | 9-5   |

|    |      | 9.2.5 Universal Flex Connector Parts List                                  | 9-5   |

|    | 9.3  | Keypad Top and Bottom Overlays                                             | 9-6   |

|    | 9.4  | Keypad Circuit Board/Schematic Diagrams and Parts List                     | 9-7   |

|    | 9.5  | Controller Circuit Board/Schematic Diagrams and Parts List                 | 9-13  |

|    | 9.6  | UHF Band 1 Circuit Board/Schematic Diagrams and Parts List                 |       |

|    |      | (PCB 8480450Z03)                                                           | 9-21  |

|    | 9.7  | UHF Band 1 Circuit Board/Schematic Diagrams and Parts List                 |       |

|    |      | (PCB 8480450Z13 / 8480587Z05)                                              | 9-33  |

|    | 9.8  | UHF Band 1 Circuit Board/Schematic Diagrams and Parts List                 |       |

|    |      | (PCB 8480450Z14)                                                           | 9-47  |

|    | 9.9  | UHF Band 1 Circuit Board/Schematic Diagrams and Parts List                 | 0.07  |

|    | 0.40 | (PCB 8486458Z02)                                                           | 9-67  |

|    | 9.10 | UHF Band 1 Circuit Board/Schematic Diagrams and Parts List                 | 0.04  |

|    | 0 11 | (PCB 8486458Z03)UHF 1 Band Circuit Board/Schematic Diagrams and Parts List | 9-0 1 |

|    | 9.11 | (PCB 8415234H01)                                                           | 0_101 |

|    | 0 12 | UHF Band 1 Circuit Board/Schematic Diagrams and Parts List                 |       |

|    |      | UHF Band 2 Circuit Board/Schematic Diagrams and Parts List                 | 5-120 |

|    | 5.10 | (PCB 8485641Z02)                                                           | 9-135 |

|    | 9.14 | UHF Band 2 Circuit Board/Schematic Diagrams and Parts List                 | 0 100 |

|    | 0    | (PCB 8485641Z06 / 8485677Z03)                                              | 9-147 |

|    | 9.15 | UHF Band 2 Circuit Board/Schematic Diagrams and Parts List                 |       |

|    |      | (PCB 8486686Z01)                                                           | 9-161 |

|    | 9.16 | UHF Band 2 Circuit Board/Schematic Diagrams and Parts List                 |       |

|    |      | (PCB 8486686Z02)                                                           | 9-175 |

|    | 9.17 | UHF Band 2 Circuit Board/Schematic Diagrams and Parts List                 |       |

|    |      | (PCB 8415235H01)                                                           |       |

|    | 9.18 | UHF Band 2 Circuit Board/Schematic Diagrams and Parts List                 | 9-217 |

Table of Contents ix

|    | 9.19 | VHF Circuit Board/Schematic Diagrams and Parts List (PCB 8486062B09)     | 9-229 |

|----|------|--------------------------------------------------------------------------|-------|

|    | 9.20 | VHF Circuit Board/Schematic Diagrams and Parts List (PCB 8486062B12)     | 9-241 |

|    | 9.21 | VHF Circuit Board/Schematic Diagrams and Parts List                      |       |

|    |      | (PCB 8486062B16 / 8486062B17 / 8486101B11)                               | 9-253 |

|    | 9.22 | VHF Circuit Board/Schematic Diagrams and Parts List (PCB 8486473Z03)     | 9-269 |

|    | 9.23 | VHF Circuit Board/Schematic Diagrams and Parts List (PCB 8486473Z04)     | 9-283 |

|    | 9.24 | VHF Circuit Board/Schematic Diagrams and Parts List (PCB 8415112H01)     | 9-303 |

|    | 9.25 | VHF Circuit Board/Schematic Diagrams and Parts List                      | 9-325 |

|    | 9.26 | Low Band Circuit Board/Schematic Diagrams and Parts List                 | 9-337 |

|    | 9.27 | 800 MHz Circuit Board/Schematic Diagrams and Parts List                  |       |

|    |      | (PCB 84860641Z02 / 8480641Z03 (Rev B)                                    | 9-353 |

|    | 9.28 | PassPort Circuit Board/Schematic Diagram                                 | 9-373 |

|    | 9.29 | 900 MHz Circuit Board/Schematic Diagrams and Parts List (PCB 8485910Z01) | 9-375 |

| ΑĮ | open | dix A Replacement Parts Ordering                                         | A-1   |

|    | A.1  | Basic Ordering Information                                               | A-1   |

|    | A.2  | Transceiver Board and VOCON Board Ordering Information                   |       |

|    | A.3  | Motorola Online                                                          | A-1   |

|    | A.4  | Mail Orders                                                              | A-1   |

|    | A.5  | Telephone Orders                                                         | A-2   |

|    | A.6  | Fax Orders                                                               | A-2   |

|    | A.7  | Parts Identification                                                     | A-2   |

|    | A.8  | Product Customer Service                                                 | A-2   |

Table of Contents

List of Figures xi

# **List of Figures**

| Figure 2-1. [ | DC Power Distribution Block Diagram                           | . 2-1 |

|---------------|---------------------------------------------------------------|-------|

| Figure 3-1. k | Keypad Block Diagram                                          | . 3-1 |

| Figure 3-2. ( | Controller Block Diagram                                      | . 3-2 |

| Figure 3-3. F | RTC Circuit                                                   | 3-3   |

| Figure 4-1.   | Fransmitter Block Diagram                                     | . 4-1 |

| Figure 4-2. \ | JHF Receiver Block Diagram                                    | . 4-3 |

| Figure 4-3. F | Frequency Generation Unit Block Diagram                       | . 4-4 |

| Figure 4-4. S | Synthesizer Block Diagram                                     | . 4-5 |

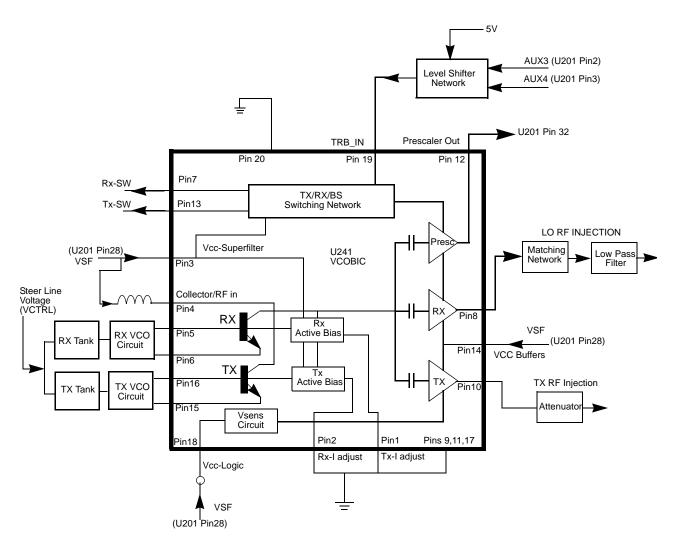

| Figure 4-5. \ | VCO Block Diagram                                             | . 4-6 |

| Figure 5-1.   | Fransmitter Block Diagram                                     | . 5-1 |

| Figure 5-2. \ | JHF Receiver Block Diagram                                    | . 5-3 |

| Figure 5-3. F | Frequency Generation Unit Block Diagram                       | . 5-4 |

| Figure 5-4. S | Synthesizer Block Diagram                                     | . 5-5 |

| Figure 5-5. \ | VCO Block Diagram                                             | . 5-6 |

| Figure 6-1.   | Fransmitter Block Diagram                                     | 6-1   |

| Figure 6-2. \ | VHF Receiver Block Diagram                                    | 6-3   |

| Figure 6-3. \ | VHF Receiver Block Diagram                                    | 6-5   |

| Figure 6-4. F | Frequency Generation Unit Block Diagram                       | 6-8   |

| Figure 6-5.   | Synthesizer Block Diagram                                     | 6-9   |

| Figure 6-6. \ | VCO Block Diagram                                             | 6-10  |

| Figure 7-1. L | _ow Band Transmitter Block Diagram                            | . 7-1 |

| Figure 7-2. L | _ow Band Receiver Block Diagram                               | . 7-3 |

| Figure 7-3. L | Low Band Frequency Generation Unit Block Diagram              | . 7-5 |

| Figure 7-4. L | Low Band Synthesizer Block Diagram                            | . 7-6 |

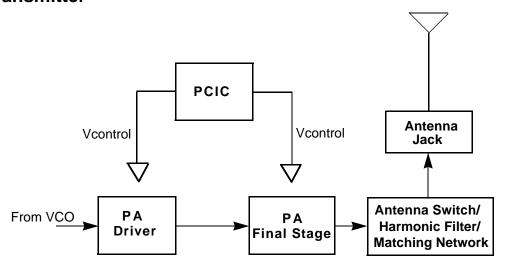

|               | B00 MHz Transmitter Block Diagram                             |       |

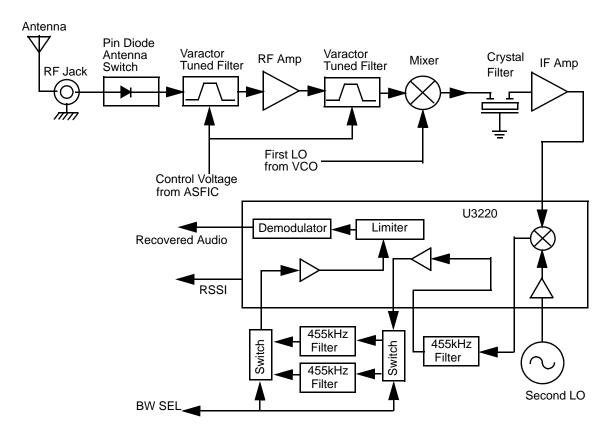

| Figure 7-6. 8 | 300 MHz Receiver Block Diagram                                | . 7-9 |

| Figure 7-7. 8 | 300 MHz Frequency Generation Unit Block Diagram               | 7-11  |

| Figure 7-8. 8 | 300 MHz Synthesizer Block Diagram                             | 7-12  |

|               | 300 MHz VCO Block Diagram                                     |       |

|               | Transmitter Block Diagram                                     |       |

| Figure 7-11.  | 900 MHz Receiver Block Diagram                                | 7-18  |

| Figure 7-12.  | Frequency Generation Unit Block Diagram                       | 7-21  |

| Figure 7-13.  | Synthesizer Block Diagram                                     | 7-23  |

| Figure 7-14.  | VCO Block Diagram                                             | 7-24  |

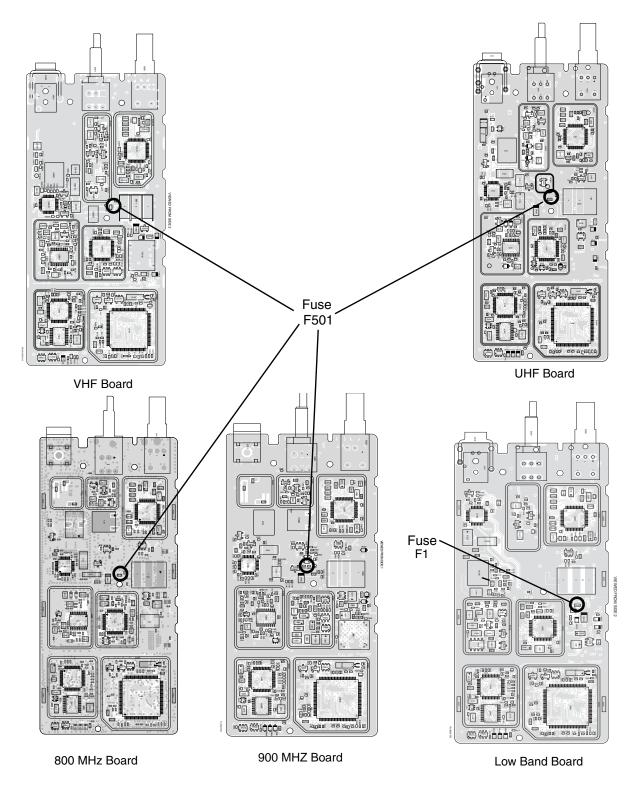

| Figure 8-1. \ | JHF/VHF/Low Band/800 MHz/900 MHz Circuit Board Fuse Locations | 8-6   |

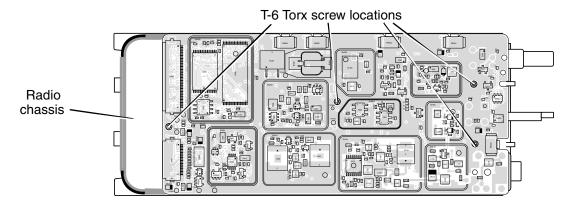

| Figure 8-2. ( | Circuit Board Removal and Reinstallation                      | . 8-7 |

|               | Keypad-Controller Interconnect Flex                           |       |

| Figure 9-2. k | Keypad-Controller Interconnect Flex Schematic Diagram         | . 9-3 |

|               | Jniversal Flex Connector                                      |       |

| Figure 9-4. \ | Jniversal Flex Connector Schematic Diagram                    | . 9-5 |

| Figure 9-5. k | Keypad Top and Bottom Board Overlays                          | . 9-6 |

| Figure 9-6. k | Keypad Board (5000 and 7000 Series) Schematic Diagram         | . 9-7 |

| Figure 9-7. 9 | 9000 Series Keypad Top and Bottom Board Overlays              | . 9-9 |

| Figure 9-8. 9 | 9000 Series Keypad Board Schematic Diagram                    | 9-10  |

| •             | VHF/UHF Complete Controller Schematic Diagram                 |       |

| Figure 9-10.  | VHF/UHF Controller ASFIC/ON_OFF Schematic Diagram             | 9-14  |

|               | VHF/UHF Controller ASFIC/ON_OFF Schematic Diagram             |       |

| Figure 9-12.  | VHF/UHF Controller Microprocessor Schematic Diagram           | 9-16  |

xii List of Figures

|              |                        | Microprocessor Schematic Diagram                   |                   |

|--------------|------------------------|----------------------------------------------------|-------------------|

| Figure 9-14. | Controller Memory So   | chematic Diagram                                   | 9-18              |

| Figure 9-15. | Controller Audio Powe  | er Amplifier Schematic Diagram                     | 9-19              |

| Figure 9-16. | Controller Interface S | chematic Diagram                                   | 9-20              |

| Figure 9-17. | UHF (403-470 MHz) 5    | 5000/7000 Series Main Board Top Side               |                   |

|              |                        | ·                                                  | 9-21              |

| Figure 9-18. | UHF (403-470 MHz) 5    | 5000/7000 Series Main Board Bottom Side            |                   |

| PCB 8480     | 450Z03                 |                                                    | 9-22              |

| Figure 9-19. | UHF (403-470 MHz) (    | Controls and Switches Schematic Diagram            | 9-23              |

|              |                        | Receiver Front End Schematic Diagram               |                   |

|              |                        | Receiver Back End Schematic Diagram                |                   |

| Figure 9-22. | UHF (403-470 MHz) \$   | Synthesizer Schematic Diagram                      | 9-26              |

| Figure 9-23. | UHF (403-470 MHz) \    | Voltage Controlled Oscillator Schematic Diagram    | 9-27              |

|              |                        | Transmitter Schematic Diagram                      |                   |

| •            |                        | 5000/7000 Series Main Board Top Side               |                   |

|              |                        |                                                    | 9-33              |

| Figure 9-26. | UHF (403-470 MHz) 5    | 5000/7000 Series Main Board Bottom Side            |                   |

|              |                        |                                                    | 9-34              |

|              |                        | 5000/7000 Series Main Board Top Side PCB           |                   |

| -            | 05                     | · · · · · · · · · · · · · · · · · · ·              | 9-35              |

|              |                        | 5000/7000 Series Main Board Bottom Side            |                   |

| •            | ,                      |                                                    | 9-36              |

|              |                        | Controls and Switches Schematic Diagram            |                   |

|              |                        | Receiver Front End Schematic Diagram               |                   |

| •            |                        | Receiver Back End Schematic Diagram                |                   |

|              |                        | Synthesizer Schematic Diagram                      |                   |

|              |                        | Voltage Controlled Oscillator Schematic Diagram    |                   |

|              |                        | Transmitter Schematic Diagram                      |                   |

| •            |                        | 5000/7000 Series Main Board Top Side               | J 72              |

| •            | •                      |                                                    | 9-47              |

|              |                        | 5000/7000 Series Main Board Bottom Side            | 3- <del>4</del> 1 |

| •            | •                      |                                                    | 0_18              |

|              |                        | Controls And Switches Schematic Diagram            |                   |

|              |                        | Receiver Front End Schematic Diagram               |                   |

|              |                        | Receiver Back End Schematic Diagram                |                   |

|              |                        | Synthesizer Schematic Diagram                      |                   |

|              |                        | Voltage Controlled Oscillator Schematic Diagram    |                   |

|              |                        | Harmonic Filter Schematic Diagram                  |                   |

|              |                        | Transmitter Schematic Diagram                      |                   |

|              |                        |                                                    |                   |

|              |                        | Complete Controller Schematic Diagram              |                   |

|              |                        | Controller ASFIC/ON_OFF Schematic Diagram          |                   |

| •            | ,                      | Controller Microprocessor Schematic Diagram        |                   |

| •            | ,                      | Controller Memory Schematic Diagram                |                   |

| •            |                        | Controller Audio Power Amplifier Schematic Diagram |                   |

|              |                        | Controller Interface Schematic Diagram             | 9-61              |

| •            | ,                      | 5000/7000 Series Main Board Top Side               |                   |

|              |                        |                                                    | 9-67              |

| •            | ,                      | 5000/7000 Series Main Board Bottom Side            | _                 |

|              |                        |                                                    |                   |

| •            |                        | Controls And Switches Schematic Diagram            |                   |

| •            |                        | Receiver Front-End Schematic Diagram               |                   |

| Figure 9-54. | UHF (403-470 MHz) F    | Receiver Back-End Schematic Diagram                | 9-71              |

List of Figures xiii

| Figure 9-55. UHF (403-470 MHz) Synthesizer Schematic Diagram                      | . 9-72 |

|-----------------------------------------------------------------------------------|--------|

| Figure 9-56. UHF (403-470 MHz) Voltage Controlled Oscillator Schematic Diagram    | . 9-73 |

| Figure 9-57. UHF (403-470 MHz) Harmonic Filter Schematic Diagram                  | . 9-74 |

| Figure 9-58. UHF (403-470 MHz) Transmitter Schematic Diagram                      |        |

| Figure 9-59. UHF (403-470 MHz) Controller ASFIC/ON_OFF Schematic Diagram          | . 9-76 |

| Figure 9-60. UHF (403-470 MHz) 5000/7000 Series Main Board Top Side               |        |

| PCB No. 8486458Z03                                                                | . 9-81 |

| Figure 9-61. UHF (403-470 MHz) 5000/7000 Series Main Board Bottom Side            |        |

| PCB No. 8486458Z03                                                                |        |

| Figure 9-62. UHF (403-470 MHz) Controls And Switches Schematic Diagram            |        |

| Figure 9-63. UHF (403-470 MHz) Receiver Front End Schematic Diagram               |        |

| Figure 9-64. UHF (403-470 MHz) Receiver Back End Schematic Diagram                |        |

| Figure 9-65. UHF (403-470 MHz) Synthesizer Schematic Diagram                      |        |

| Figure 9-66. UHF (403-470 MHz) Voltage Controlled Oscillator Schematic Diagram    |        |

| Figure 9-67. UHF (403-470 MHz) Harmonic Filter Schematic Diagram                  |        |

| Figure 9-68. UHF (403-470 MHz) Transmitter Schematic Diagram                      |        |

| Figure 9-69. UHF (403-470 MHz) Complete Controller Schematic Diagram              | . 9-90 |

| Figure 9-70. UHF (403-470 MHz) Controller ASFIC/ON_OFF Schematic Diagram          | . 9-91 |

| Figure 9-71. UHF (403-470 MHz) Controller Microprocessor Schematic Diagram        | . 9-92 |

| Figure 9-72. UHF (403-430 MHz) Controller Memory Schematic Diagram                | . 9-93 |

| Figure 9-73. UHF (403-470 MHz) Controller Audio Power Amplifier Schematic Diagram | . 9-94 |

| Figure 9-74. UHF (403-470 MHz) Controller Interface Schematic Diagram             | . 9-95 |

| Figure 9-75. UHF (403-470 MHz) Main Board Top Side PCB No. 8415234H01             | 9-101  |

| Figure 9-76. UHF (403-470 MHz) Main Board Bottom Side PCB No. 8415234H01          | 9-102  |

| Figure 9-77. UHF Controls And Switches Schematic Diagram                          |        |

| Figure 9-78. UHF Receiver Front End Schematic Diagram                             |        |

| Figure 9-79. UHF Receiver Back End Schematic Diagram                              |        |

| Figure 9-80. UHF Synthesizer Schematic Diagram                                    |        |

| Figure 9-81. UHF Voltage Controlled Oscillator Schematic Diagram                  |        |

| Figure 9-82. UHF Harmonic Filter Schematic Diagram                                |        |

| Figure 9-83. UHF Transmitter Schematic Diagram                                    |        |

| Figure 9-84. Complete Controller Schematic Diagram                                |        |

| Figure 9-85. Controller ASFIC/ON_OFF Schematic Diagram                            |        |

| Figure 9-86. Controller Microprocessor Schematic Diagram                          |        |

| Figure 9-87. Controller Memory Schematic Diagram                                  |        |

| Figure 9-88. Controller Audio Power Amplifier Schematic Diagram                   |        |

| Figure 9-89. Controller Interface Schematic Diagram                               |        |

| Figure 9-90. UHF (403-470 MHz) 9000 Series Main Board Top Side PCB                |        |

| Figure 9-91. UHF (403-470 MHz) 9000 Series Main Board Bottom Side PCB             |        |

| Figure 9-92. UHF (403-470 MHz) Controls and Switches Schematic Diagram            |        |

| Figure 9-93. UHF (403-470 MHz) Receiver Front End Schematic Diagram               |        |

| Figure 9-94. UHF (403-470 MHz) Receiver Back End Schematic Diagram                |        |

| Figure 9-95. UHF (403-470 MHz) Synthesizer Schematic Diagram                      |        |

| Figure 9-96. UHF (403-470 MHz) Voltage Controlled Oscillator Schematic Diagram    |        |

|                                                                                   |        |

| Figure 9-97. UHF (403-470 MHz) Transmitter Schematic Diagram                      | 9-130  |

| Figure 9-98. UHF (450-527 MHz) 5000/7000 Series Main Board Top Side               | 0.125  |

| PCB 8485641Z02                                                                    | 9-133  |

| Figure 9-99. UHF (450-527 MHz) 5000/7000 Series Main Board Bottom Side            | 0.400  |

| PCB 8485641Z02                                                                    |        |

| Figure 9-100. UHF (450-527 MHz) Controls and Switches Schematic Diagram           |        |

| Figure 9-101. UHF (450-527 MHz) Receiver Front End Schematic Diagram              |        |

| Figure 9-102. UHF (450-527 MHz) Receiver Back End Schematic Diagram               |        |

| Figure 9-103. UHF (450-527 MHz) Synthesizer Schematic Diagram                     | 9-140  |

xiv List of Figures

|                 | UHF (450-527 MHz) Voltage Controlled Oscillator Schematic Diagram                      |       |

|-----------------|----------------------------------------------------------------------------------------|-------|

| •               | UHF (450-527 MHz) Transmitter Schematic Diagram                                        | 9-142 |

| •               | UHF (450-527 MHz) 5000/7000 Series Main Board Top Side 41Z06                           | 9-147 |

| Figure 9-107.   | UHF (450-527 MHz) 5000/7000 Series Main Board Bottom Side                              |       |

| PCB 84856       | 41Z06                                                                                  | 9-148 |

| Figure 9-108.   | UHF (450-527 MHz) 5000/7000 Series Main Board Top Side                                 |       |

| PCB 84856       | 77Z03                                                                                  | 9-149 |

| Figure 9-109.   | UHF (450-527 MHz) 5000/7000 Series Main Board Bottom Side                              |       |

| PCB 84866       | 77Z03                                                                                  | 9-150 |

| Figure 9-110.   | UHF (450-527 MHz) Controls and Switches Schematic Diagram                              | 9-151 |

| Figure 9-111.   | UHF (450-527 MHz) Receiver Front End Schematic Diagram                                 | 9-152 |

| Figure 9-112.   | UHF (450-527 MHz) Receiver Back End Schematic Diagram                                  | 9-153 |

| Figure 9-113.   | UHF (450-527 MHz) Synthesizer Schematic Diagram                                        | 9-154 |

|                 | UHF (450-527 MHz) Voltage Controlled Oscillator Schematic Diagram                      |       |

| •               | UHF (450-527 MHz) Transmitter Schematic Diagram                                        |       |

| •               | UHF (450-527 MHz) 5000/7000 Series Main Board Top Side                                 |       |

|                 | l86686Z01                                                                              | 9-161 |

|                 | UHF (450-527 MHz) 5000/7000 Series Main Board Bottom Side                              |       |

| -               | l86686Z01                                                                              | 9-162 |

|                 | UHF (450-527 MHz) Controls and Switches Schematic Diagram                              |       |

|                 | UHF (450-527 MHz) Receiver Front End Schematic Diagram                                 |       |

|                 | UHF (450-527 MHz) Receiver Back End Schematic Diagram                                  |       |

|                 | UHF (450-527 MHz) Synthesizer Schematic Diagram                                        |       |

| •               | UHF (450-527 MHz) Voltage Controlled Oscillator Schematic Diagram                      |       |

|                 | UHF (450-527 MHz) Harmonic Filter Schematic Diagram                                    |       |

|                 | UHF (450-527 MHz) Transmitter Schematic Diagram                                        |       |

|                 | UHF (450-527 MHz) Controller ASFIC/ON_OFF Schematic Diagram                            |       |

|                 | UHF (450-527 MHz) 5000/7000 Series Main Board Top Side                                 | 0     |

|                 | 186686Z02                                                                              | 9-175 |

|                 | UHF (450-527 MHz) 5000/7000 Series Main Board Bottom Side                              | 0     |

| •               | 186686Z02                                                                              | 9-176 |

|                 | UHF (450-527 MHz) Controls And Switches Schematic Diagram                              |       |

|                 | UHF (450-527 MHz) Receiver Front End Schematic Diagram                                 |       |

|                 | UHF (450-527 MHz) Receiver Back End Schematic Diagram                                  |       |

|                 | UHF (450-527 MHz) Synthesizer Schematic Diagram                                        |       |

|                 | UHF (450-527 MHz) Voltage Controlled Oscillator Schematic Diagram                      |       |

|                 | UHF (450-527 MHz) Harmonic Filter Schematic Diagram                                    |       |

| •               | UHF (450-527 MHz) Transmitter Schematic Diagram                                        |       |

| •               | UHF (450-527 MHz) Complete Controller Schematic Diagram                                |       |

|                 | UHF (450-527 MHz) Controller ASFIC/ON_OFF Schematic Diagram                            |       |

| •               | UHF (450-527 MHz) Controller Microprocessor Schematic Diagram                          |       |

| •               | UHF (450-527 MHz) Controller Memory Schematic Diagram                                  |       |

| •               | UHF (450-527 MHz) Controller Audio Power Amplifier Schematic Diagram                   |       |

|                 |                                                                                        |       |

|                 | UHF (450-527 MHz) Controller Interface Schematic Diagram                               |       |

|                 | UHF Band 2 (450-527 MHz) Main Board Top Side PCB No. 8415235H01                        | 3-133 |

| •               | UHF Band 2 (450-527 MHz) Main Board Bottom Side                                        | 0.400 |

|                 | 115235H01                                                                              |       |

|                 | UHF Band 2 Controls And Switches Schematic Diagram                                     |       |

|                 | UHF Band 2 Receiver Front End Schematic Diagram                                        |       |

| •               | UHF Band 2 Receiver Back End Schematic DiagramUHF Band 2 Synthesizer Schematic Diagram |       |

| 1 1401 C 3-140. | ULII DANU Z OYNUICOIZEI OUIEINAUU DIAYLAIN                                             | コームしし |

List of Figures xv

|               | UHF Band 2 Voltage Controlled Oscillator Schematic Diagram        |       |

|---------------|-------------------------------------------------------------------|-------|

| •             | UHF Band 2 Harmonic Filter Schematic Diagram                      |       |

| •             | UHF Band 2 Transmitter Schematic Diagram                          |       |

|               | Complete Controller Schematic Diagram                             |       |

|               | Controller ASFIC/ON_OFF Schematic Diagram                         |       |

| •             | Controller Microprocessor Schematic Diagram                       |       |

| •             | Controller Memory Schematic Diagram                               |       |

|               | Controller Audio Power Amplifier Schematic Diagram                |       |

|               | Controller Interface Schematic Diagram                            |       |

|               | UHF (450-527 MHz) 9000 Series Main Board Top Side PCB             |       |

|               | UHF (450-527 MHz) 9000 Series Main Board Bottom Side PCB          |       |

| •             | UHF (450-527 MHz) Controls and Switches Schematic Diagram         |       |

| •             | UHF (450-527 MHz) Receiver Front End Schematic Diagram            |       |

| •             | UHF (450-527 MHz) Receiver Back End Schematic Diagram             |       |

|               | UHF (450-527 MHz) Synthesizer Schematic Diagram                   |       |

|               | UHF (450-527 MHz) Voltage Controlled Oscillator Schematic Diagram |       |

| •             | UHF (450-527 MHz) Transmitter Schematic Diagram                   |       |

| •             | UHF (450-527 MHz) Voice Storage Schematic Diagram                 | 9-225 |

| •             | VHF (136-174 MHz) 5000/7000 Series Main Board Top Side            |       |

|               | 62B09                                                             | 9-229 |

| •             | VHF (136-174 MHz) 5000/7000 Series Main Board Bottom Side         |       |

|               | 62B09                                                             |       |

| Figure 9-167. | VHF (136-174 MHz) Controls and Switches Schematic Diagram         | 9-231 |

|               | VHF (136-174 MHz) Receiver Front End Schematic Diagram            |       |

| Figure 9-169. | VHF (136-174 MHz) Receiver Back End Schematic Diagram             | 9-233 |

| Figure 9-170. | VHF (136-174 MHz) Synthesizer Schematic Diagram                   | 9-234 |

| Figure 9-171. | VHF (136-174 MHz) Voltage Controlled Oscillator Schematic Diagram | 9-235 |

| Figure 9-172. | VHF (136-174 MHz) Transmitter Schematic Diagram                   | 9-236 |

| Figure 9-173. | VHF (136-174 MHz) 5000/7000 Series Main Board Top Side            |       |

|               | 62B12                                                             | 9-241 |

| Figure 9-174. | VHF (136-174 MHz) 5000/7000 Series Main Board Bottom Side         |       |

|               | 62B12                                                             | -     |

|               | VHF (136-174 MHz) Controls and Switches Schematic Diagram         |       |

| Figure 9-176. | VHF (136-174 MHz) Receiver Front End Schematic Diagram            | 9-244 |

|               | VHF (136-174 MHz) Receiver Back End Schematic Diagram             |       |

|               | VHF (136-174 MHz) Synthesizer Schematic Diagram                   |       |

| Figure 9-179. | VHF (136-174 MHz) Voltage Controlled Oscillator Schematic Diagram | 9-247 |

| Figure 9-180. | VHF (136-174 MHz) Transmitter Schematic Diagram                   | 9-248 |

|               | VHF (136-174 MHz) 5000/7000 Series Main Board Top Side            |       |

| PCB 84860     | 62B16                                                             | 9-253 |

| Figure 9-182. | VHF (136-174 MHz) 5000/7000 Series Main Board Bottom Side         |       |

|               | 62B16                                                             | 9-254 |

| Figure 9-183. | VHF (136-174 MHz) 5000/7000 Series Main Board Top Side            |       |

| PCB 84860     | 62B17                                                             | 9-255 |

| Figure 9-184. | VHF (136-174 MHz) 5000/7000 Series Main Board Bottom Side         |       |

| -             | 62B17                                                             | 9-256 |

| Figure 9-185. | VHF (136-174 MHz) 5000/7000 Series Main Board Top Side            |       |

| PCB 84861     | 01B11                                                             | 9-257 |

| Figure 9-186. | VHF (136-174 MHz) 5000/7000 Series Main Board Bottom Side         |       |

| •             | 01B11                                                             | 9-258 |

|               | VHF (136-174 MHz) Controls and Switches Schematic Diagram         |       |

|               | VHF (136-174 MHz) Receiver Front End Schematic Diagram            |       |

|               | VHF (136-174 MHz) Receiver Back End Schematic Diagram             |       |

xvi List of Figures

| Figure 9-190. | VHF (136-174 MHz) Synthesizer Schematic Diagram                      | 9-262 |

|---------------|----------------------------------------------------------------------|-------|

| Figure 9-191. | VHF (136-174 MHz) Voltage Controlled Oscillator Schematic Diagram    | 9-263 |

| •             | VHF (136-174 MHz) Transmitter Schematic Diagram                      | 9-264 |

| •             | VHF (136-174 MHz) 5000/7000 Series Main Board Top Side               |       |

| PCB No. 84    | l86473Z03                                                            | 9-269 |

|               | VHF (136-174 MHz) 5000/7000 Series Main Board Bottom Side            |       |

|               | l86473Z03                                                            |       |

|               | VHF (136-174 MHz) Controls And Switches Schematic Diagram            |       |

|               | VHF (136-174 MHz) Receiver Front-End Schematic Diagram               |       |

| •             | VHF (136-174 MHz) Receiver Back-End Schematic Diagram                |       |

| •             | VHF (136-174 MHz) Synthesizer Schematic Diagram                      |       |

| •             | VHF (136-174 MHz) Voltage Controlled Oscillator Schematic Diagram    |       |

| •             | VHF (136-174 MHz) Transmitter Schematic Diagram                      |       |

| •             | VHF (136-174 MHz) Controller ASFIC/ON_OFF Schematic Diagram          | 9-277 |

|               | VHF (136-174 MHz) 5000/7000 Series Main Board Top Side               | 0.000 |

|               | 186473Z04                                                            | 9-283 |

| -             | VHF (136-174 MHz) 5000/7000 Series Main Board Bottom Side            | 0.004 |

|               | 186473Z04                                                            |       |

| -             | VHF (136-174 MHz) Controls And Switches Schematic Diagram            |       |

|               | VHF (136-174 MHz) Receiver Front End Schematic Diagram               |       |

|               | VHF (136-174 MHz) Receiver Back End Schematic Diagram                |       |

| -             | VHF (136-174 MHz) Synthesizer Schematic Diagram                      |       |

| •             | VHF (136-174 MHz) Voltage Controlled Oscillator Schematic Diagram    |       |

| _             | VHF (136-174 MHz) Complete Controller Schematic Diagram              |       |

| -             | VHF (136-174 MHz) Complete Controller Schematic Diagram              |       |

| •             | VHF (136-174 MHz) Controller ASFIC/ON_OFF Schematic Diagram          |       |

| _             | VHF (136-174 MHz) Controller Microprocessor Schematic Diagram        |       |

|               | VHF (136-174 MHz) Controller Memory Schematic Diagram                |       |

|               | VHF (136-174 MHz) Controller Audio Power Amplifier Schematic Diagram |       |

|               | VHF (136-174 MHz) Controller Interface Schematic Diagram             |       |

|               | VHF (136-174 MHz) Main Board Top Side PCB No. 8415112H01             |       |

| •             | VHF (136-174 MHz) Main Board Bottom Side PCB No. 8415112H01          |       |

| •             | VHF Controls And Switches Schematic Diagram                          |       |

|               | VHF Receiver Front End Schematic Diagram                             |       |

|               | VHF Receiver Back End Schematic Diagram                              |       |

|               | VHF Synthesizer Schematic Diagram                                    |       |

|               | VHF Voltage Controlled Oscillator Schematic Diagram                  |       |

|               | VHF Transmitter Schematic Diagram                                    |       |

| -             | Complete Controller Schematic Diagram                                |       |

| •             | Controller ASFIC/ON_OFF Schematic Diagram                            |       |

|               | Controller Microprocessor Schematic Diagram                          |       |

|               | Controller Memory Schematic Diagram                                  |       |

| •             | Controller Audio Power Amplifier Schematic Diagram                   |       |

|               | Controller Interface Schematic Diagram                               |       |

|               | VHF (136-174 MHz) 9000 Series Main Board Top Side PCB                |       |

| •             | VHF (136-174 MHz) 9000 Series Main Board Bottom Side PCB             |       |

| •             | VHF (136-174 MHz) Controls and Switches Schematic Diagram            |       |

| •             | VHF (136-174 MHz) Receiver Front End Schematic Diagram               |       |

|               | VHF (136-174 MHz) Receiver Back End Schematic Diagram                |       |

|               | VHF (136-174 MHz) Voltage Centrelled Oscillator Schematic Diagram    |       |

|               | VHF (136-174 MHz) Voltage Controlled Oscillator Schematic Diagram    |       |

| riquie 9-23/. | VHF (136-174 MHz) Transmitter Schematic Diagram                      | 9-332 |

List of Figures xvii

| Figure 9-238. | Low Band (29.7-42/35-50 MHz) Main Board Top Side PCB               | 9-337 |

|---------------|--------------------------------------------------------------------|-------|

|               | Low Band (29.7-42/35-50 MHz) Main Board Bottom Side PCB            |       |

|               | Low Band (30-50 MHz) Controls and Switches Diagram                 |       |

|               | Low Band (29.7-42/35-50 MHz) Controller Overall Schematic Diagram  |       |

| •             | Low Band (29.7-42/35-50 MHz) Controller Memory Schematic Diagram   |       |

| •             | Low Band (29.7-42/35-50 MHz) Controller AFSIC Schematic Diagram    |       |

| •             | Low Band (29.7-42/35-50 MHz) Controller Microprocessor Schematic   |       |

|               | · · · · · · · · · · · · · · · · · · ·                              | 9-343 |

| Figure 9-245. | Low Band (29.7-42/35-50 MHz) Controller Audio PA Schematic Diagram | 9-344 |

| •             | Low Band (29.7-42/35-50 MHz) Receiver Front End Schematic Diagram  |       |

|               | Low Band (29.7-42/35-50 MHz) Receiver Back End Schematic Diagram   |       |

|               | Low Band (29.7-42/35-50 MHz) Frequency Generation Unit Synthesizer |       |

| •             | Low Band (29.7-42/35-50 MHz) Frequency Generation Unit VCO Diagram |       |

| •             | Low Band (29.7-42/35-50 MHz) Transmitter Schematic Diagram         |       |

| Figure 9-251. | 800 MHz (806-870 MHz) Main Board Top Side PCB 84860641Z02          | 9-353 |

|               | 800 MHz (806-870 MHz) Main Board Bottom Side PCB 84860641Z02       |       |

| •             | 800 MHz Popular/Preferred (806-870 MHz) Main Board Top Side        |       |

| •             | 41Z03 (Rev B)                                                      | 9-355 |

|               | 800 MHz Popular/Preferred (806-870 MHz) Main Board Bottom Side     |       |

|               | 41Z03 (Rev B)                                                      | 9-356 |

| Figure 9-255. | 800 MHz Complete Controller                                        | 9-357 |

|               | 800 MHz Controller ASFIC/ON_OFF                                    |       |

|               | 800 MHz Controller Microprocessor                                  |       |

|               | 800 MHz Controller Memory                                          |       |

| Figure 9-259. | 800 MHz Controller Audio Power Amplifier                           | 9-361 |

|               | 800 MHz Controller Interface                                       |       |

| Figure 9-261. | 800 MHz Controls and Switches Schematic Diagram                    | 9-363 |

| Figure 9-262. | 800 MHz Receiver Front End Schematic Diagram                       | 9-364 |

| Figure 9-263. | 800 MHz Receiver Back End Schematic Diagram                        | 9-365 |

| Figure 9-264. | 800 MHz Synthesizer Schematic Diagram                              | 9-366 |

| Figure 9-265. | 800 MHz Voltage Controlled Oscillator Schematic Diagram            | 9-367 |

| Figure 9-266. | 800 MHz Transmitter Schematic Diagram (Rev A)                      | 9-368 |

| Figure 9-267. | 800MHz Transmitter Schematic Diagram (Rev B)                       | 9-369 |

| Figure 9-268. | PassPort Trunking Controller PCB Board Side 1 & 2                  | 9-373 |

| Figure 9-269. | PassPort Controller Schematic Diagram                              | 9-374 |

| Figure 9-270. | 900 MHz (896-941 MHz) Main Board Top Side PCB 8485910Z01           | 9-375 |

| Figure 9-271. | 900 MHz (896-941 MHz) Main Board Bottom Side PCB 8485910Z01        | 9-376 |

|               | 900 MHz Complete Controller                                        |       |

| Figure 9-273. | 900 MHz Controller ASFIC/ON_OFF                                    | 9-378 |

| Figure 9-274. | 900 MHz Controller Microprocessor                                  | 9-379 |

| Figure 9-275. | 900 MHz Controller Memory                                          | 9-380 |

| Figure 9-276. | 900 MHz Controller Audio Power Amplifier                           | 9-381 |

| Figure 9-277. | 900 MHz Controller Interface                                       | 9-382 |

| Figure 9-278. | 900 MHz Controls and Switches Schematic Diagram                    | 9-383 |

| Figure 9-279. | 900 MHz Receiver Front End Schematic Diagram                       | 9-384 |

| Figure 9-280. | 900 MHz Receiver Back End Schematic Diagram                        | 9-385 |

| Figure 9-281. | 900 MHz Synthesizer Schematic Diagram                              | 9-386 |

| Figure 9-282. | 900 MHz Hear/Clear Schematic Diagram                               | 9-387 |

| Figure 9-283. | 900 MHz Voltage Controlled Oscillator Schematic Diagram            | 9-388 |

| Figure 9-284. | 900 MHz Transmitter Schematic Diagram                              | 9-389 |

xviii List of Figures

## **Intrinsically Safe Radio Information**

#### **FMRC Approved Equipment**